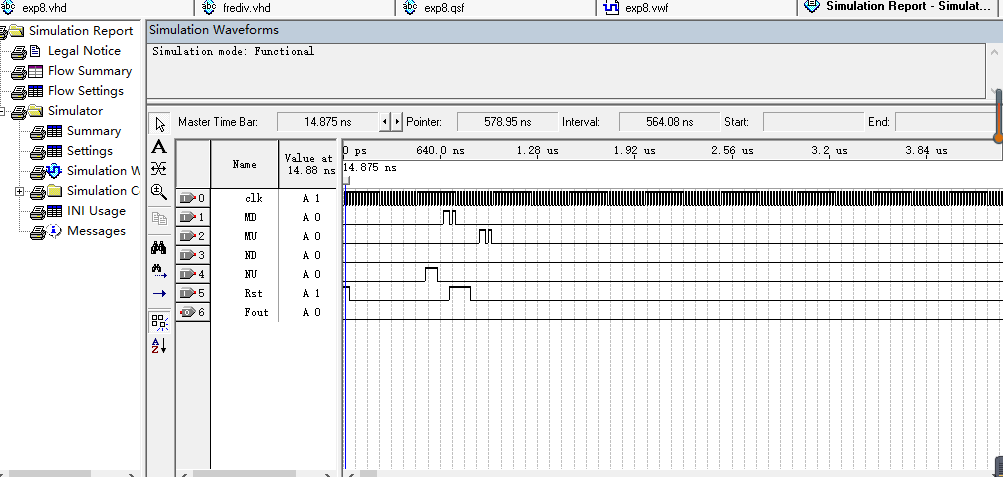

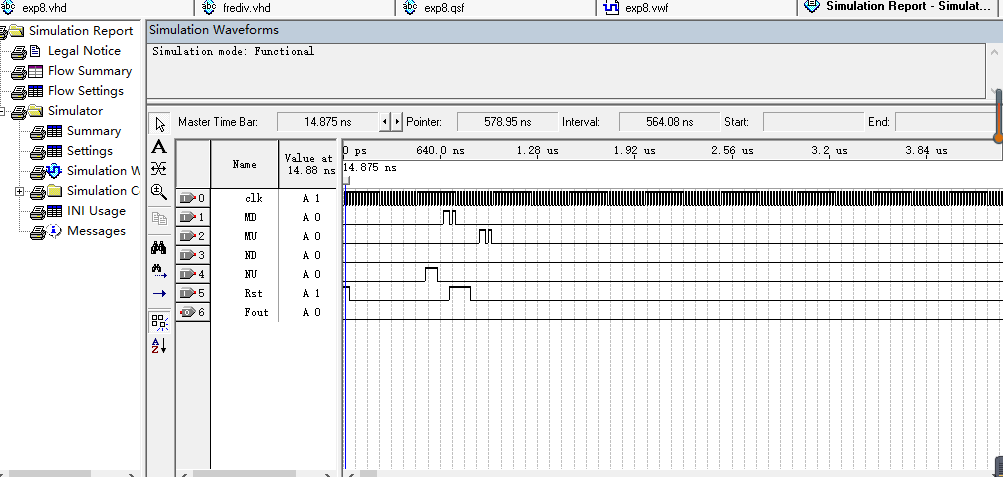

实现周期、占空比均可调的脉冲发生器。 (1)采用 1khz 的工作时钟; (2)脉冲周期 0.5s~6s,占空比 10%~90%; (3)可初始化:周期 2.5s,占空比 50%

但我改了

Time Period,Time offset,Duty cycle,

period 1 ms;Offset 0; Duty cycle 50

也把end time改为了50ms

也试过把setting 里改了functional 还是没有结果

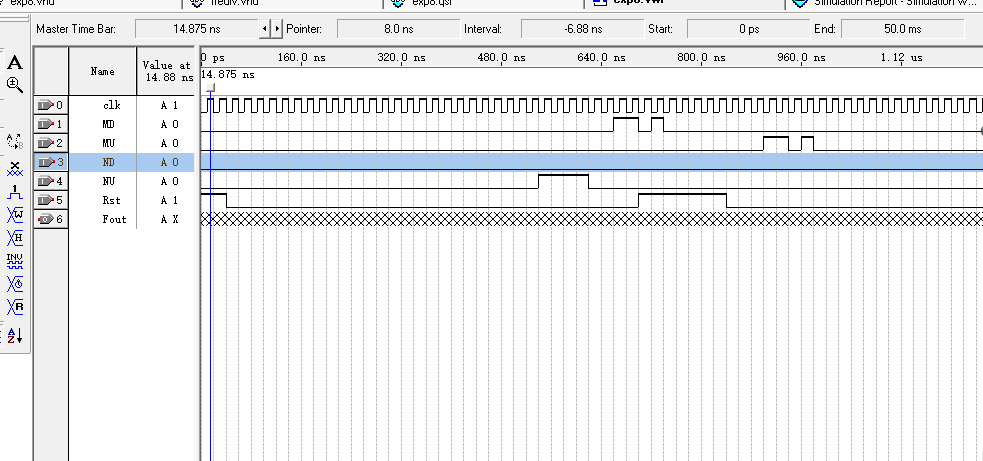

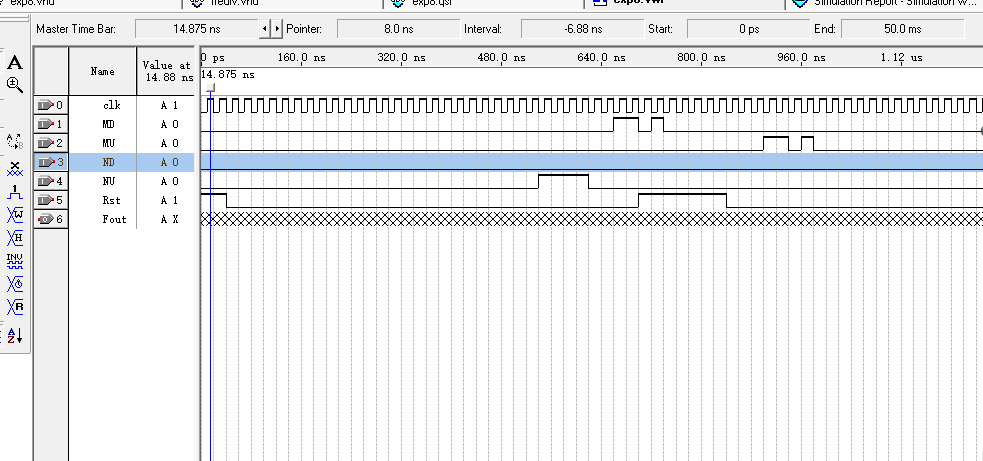

实现周期、占空比均可调的脉冲发生器。 (1)采用 1khz 的工作时钟; (2)脉冲周期 0.5s~6s,占空比 10%~90%; (3)可初始化:周期 2.5s,占空比 50%

但我改了

Time Period,Time offset,Duty cycle,

period 1 ms;Offset 0; Duty cycle 50

也把end time改为了50ms

也试过把setting 里改了functional 还是没有结果

以下回答参考 皆我百晓生、券券喵儿 等免费微信小程序相关内容作答,并由本人整理回复。

要解决这个问题,首先确保你的VHDL文件中正确地设置了工作频率(1kHz),并定义了所需的周期范围和占空比。然后,请检查你提供的设置是否适用于你的需求。

以下是修改后的exp8.vhd文件:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity exp8 is

Port ( clk, rst : in STD_LOGIC;

a0, a1 : in STD_LOGIC;

b0, b1 : in STD_LOGIC;

c0, c1 : in STD_LOGIC;

d0, d1 : in STD_LOGIC;

e0, e1 : out STD_LOGIC);

end exp8;

architecture Behavioral of exp8 is

begin

process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

a0 <= '0';

a1 <= '0';

b0 <= '0';

b1 <= '0';

c0 <= '0';

c1 <= '0';

d0 <= '0';

d1 <= '0';

e0 <= '0';

else

a0 <= '1';

a1 <= '1';

b0 <= '1';

b1 <= '1';

c0 <= '1';

c1 <= '1';

d0 <= '1';

d1 <= '1';

e0 <= '1';

end if;

end if;

end process;

a0 <= a0 and b0 and c0 and d0 and e0;

a1 <= a1 and b1 and c1 and d1 and e1;

end Behavioral;

这个版本的代码实现了一个简单的二进制计数器,每个周期内有四个输入信号(a0, a1, b0, b1)和两个输出信号(e0, e1)。你可以根据自己的需要调整这些参数以满足特定的需求。

对于占空比和周期的调整,你可以通过改变period, offset, 和duty_cycle变量来实现。例如,如果你希望周期从2.5秒变为5秒,可以将period设为500微秒,offset设为0,duty_cycle设为90%,这样就可以达到所需的结果。同样,如果你想在占空比范围内进行调整,只需相应地改变这三个参数即可。