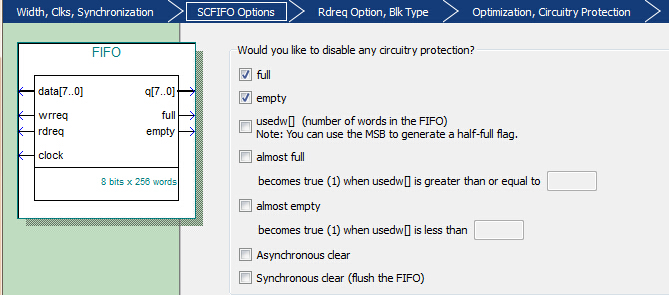

这是我用IP核生成的FIFO,测试了一下,为什么q[7:0]输出的数据全都是00啊?顶层中重实例化的FIFO:

FIFO FIFO_inst(

.clock ( clk ),

.data ( Rx_Data ),

.rdreq ( read ),

.wrreq (write),

.empty ( empty_sig ),

.full ( full_sig ),

.q ( Tx_Data )

);

串行接收数据时write=1, read =0,另外两两数据之间有个空闲时间,这时write=0, read =1,就这样交替着读写,请问有哪里错了吗?

哪位大神熟悉FPGA的FIFO操作,尤其是IP软核,帮个忙分析一下原因

- 写回答

- 好问题 0 提建议

- 追加酬金

- 关注问题

- 邀请回答

-

3条回答 默认 最新

悬赏问题

- ¥15 yolov7训练自己的数据集

- ¥15 esp8266与51单片机连接问题(标签-单片机|关键词-串口)(相关搜索:51单片机|单片机|测试代码)

- ¥15 电力市场出清matlab yalmip kkt 双层优化问题

- ¥30 ros小车路径规划实现不了,如何解决?(操作系统-ubuntu)

- ¥20 matlab yalmip kkt 双层优化问题

- ¥15 如何在3D高斯飞溅的渲染的场景中获得一个可控的旋转物体

- ¥88 实在没有想法,需要个思路

- ¥15 MATLAB报错输入参数太多

- ¥15 python中合并修改日期相同的CSV文件并按照修改日期的名字命名文件

- ¥15 有赏,i卡绘世画不出