这是设计文件代码

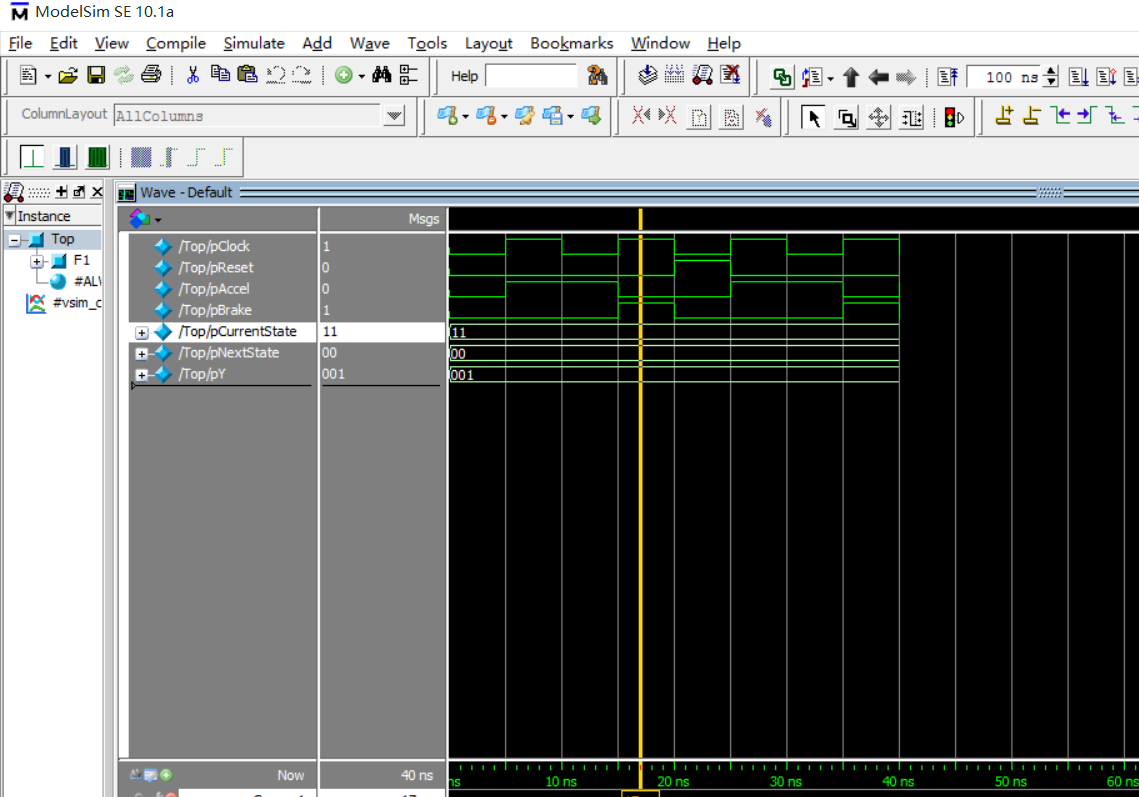

module FDG_CAO(Clock,Reset,Accel,Brake,Y);

input Clock,Reset,Accel,Brake;

output[2:0]Y;

reg[2:0]Y;

reg[1:0]CurrentState,NextState;

parameter[1:0]Stop=0,Slow=1,Medium=2,Fast=3;

always@(Accel or CurrentState)

begin:COMB

CurrentState=Stop;

NextState=Stop;

case(CurrentState)

Stop:begin

if(Accel)

NextState=Slow;

else

if(Brake)

NextState=Stop;

else

NextState=Stop;

end

Slow:begin

if(Accel)

NextState=Medium;

else

if(Brake)

NextState=Stop;

else

NextState=Slow;

end

Medium:begin

if(Accel)

NextState=Fast;

else

if(Brake)

NextState=Slow;

else

NextState=Medium;

end

Fast:begin

if(Accel)

NextState=Fast;

else

if(Brake)

NextState=Medium;

else

NextState=Fast;

end

endcase

end

always@(posedge Clock or posedge Reset)

begin:SEQ

if(Reset)

CurrentState=Stop;

else

CurrentState=NextState;

end

always@(CurrentState)

begin:OUT_LOGIC

case(CurrentState)

Stop:Y=1;

Slow:Y=2;

Medium:Y=3;

Fast:Y=4;

endcase

end

endmodule