`timescale 1ns/1ps

module freq ();

reg clk_250 = 1'b0 ;

reg rst = 1'b1 ;

reg [6 : 0] cnt = 7'd0 ;

reg valid = 1'b0 ;

reg [2 : 0] valid_cnt = 3'd0 ;

parameter PERIOD_250 = 4 ;

//产生250MHZ时钟

initial

begin

clk_250 = 0;

forever #(PERIOD_250/2) clk_250 = ~clk_250;

end

initial

begin

#8 rst = 1'b0 ;

end

always @ ( posedge clk_250 )

begin

if( rst == 1)

cnt <= 8'b0000_0000 ;

else

begin

if( cnt == 8'd100 )

cnt <= 8'd1 ;

else

cnt <= cnt + 8'b1;

end

end

always @ ( posedge clk_250 )

begin

if( rst == 1'b1 )

valid_cnt <= 3'd0 ;

else

begin

if( valid_cnt == 3'd6)

valid_cnt <= 3'd1;

else

valid_cnt <= valid_cnt + 3'd1;

end

end

always @ ( posedge clk_250 )

begin

if( rst == 1)

valid <= 1'b0 ;

else

begin

if( valid_cnt == 1)

valid <= 1'd1;

else

valid <= 1'd0;

end

end

endmodule

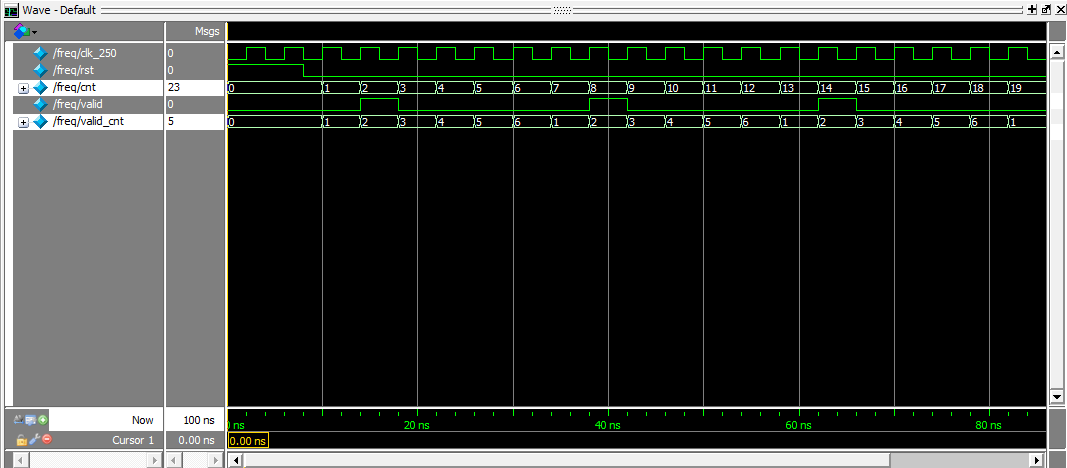

上面代码想实现的是1到100的数据进行循环。并且有一个valid信号标志有效位,每6个数据有一个valid信号。下面是我用modelsim仿真得到的仿真图。

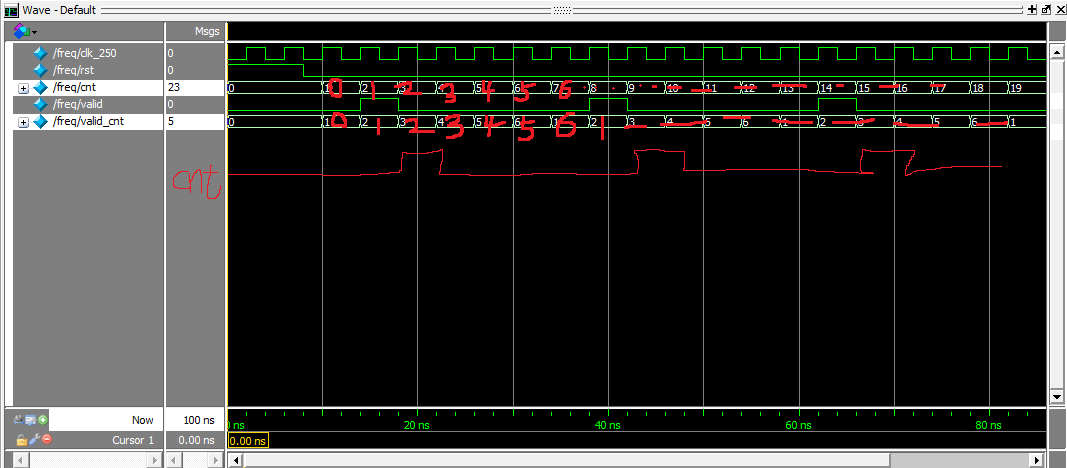

自己认为的仿真图应该是下面这样。

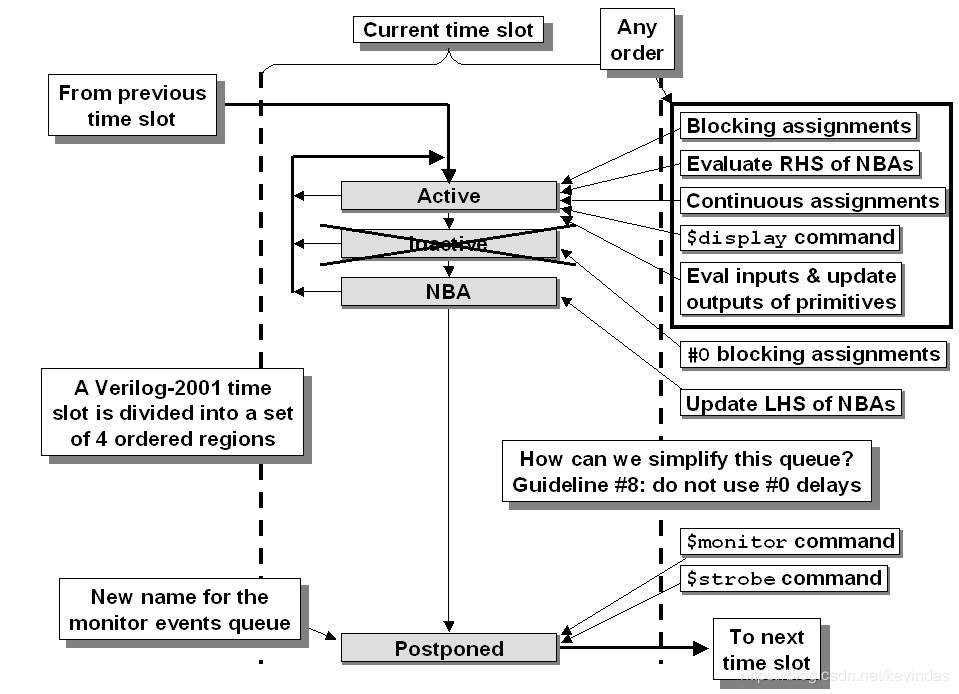

非阻塞赋值的结果要在下一个clock的上升沿才能得出。也就是需要延迟一个clock。仿真图里面感觉就有点自相矛盾。在生成cnt信号和valid-cnt 信号时直接在当前的clock就产生数据。然而产生valid信号时却是在下一个时钟产生的。

自己接触verilog时间不常工作需要,所以必须要把这个点弄会。总结上面的问题,其实就一个,非阻塞赋值会使得到的数据延时一个clock吗?如果是如何解释cnt和valid-cnt信号的生成。如果不延时一个clock那么valid信号为什么在下一clock才得出结果。希望能够得到专业的回答!!!毕竟我写了这么多又做了这么多的工作。