在modelsim上编译了一遍但错误都不会改 刚学所以有的问题还很幼稚 拜托大家了

module count(outa,clk,ud,qout,cout,data,load,cin,reset,a,b,c,d,e,f,g);

output[1:0] outa;

output[19:0] qout;

output cout;

output a,b,c,d,e,f,g;

output LAMP;

input clk,ud,load,cin;

input[19:0] data;

wire[1:0] outa;

wire[19:0] qout;

reg reset;

reg load;

wire LAMP;

reg cin;

reg data;

reg ud;

wire a,b,c,d,e,f,g;

always @(posedge clk)

begin

if(reset==1) outa<=0;

if(cin==0)

begin

if(ud)

outa<=outa+1;

else outa<=outa-1;

end

end

case(outa)

0:begin LAMP=4'b0001;end

1:begin LAMP=4'b0010;end

2:begin LAMP=4'b0100;end

3:begin LAMP=4'b1000;end

default:LAMP=4'b1000;

endcase

always @(posedge clk)

begin

if(reset) qout<=0;

else if(load) qout<=data;

if(cin)

begin

if(ud)

begin

if(outa==0)

begin

if(qout[3:0]==9)

begin

if(qout[19:4]>=1999) qout[19:4]<=1999;

else

begin

qout[3:0]<=0;qout[19:4]<=qout[19:4]+1;

end

end

else

qout[3:0]<=qout[3:0]+1;

end

else if(outa==1)

begin

if(qout[7:4]==9)

begin

if(qout[19:8]>=199) qout[19:8]<=199;

else

begin

qout[7:4]<=0;qout[19:8]<=qout[19:8]+1;

end

end

else

qout[7:4]<=qout[7:4]+1;

end

else if(outa==2)

begin

if(qout[11:8]==9)

begin

if(qout[19:12]>=19) qout[19:12]<=19;

else

begin

qout[11:8]<=0;qout[19:12]<=qout[19:12]+1;

end

end

else

qout[11:8]<=qout[11:8]+1;

end

else

begin

if(qout[15:12]==9)

begin

if(qout[19:16]>=1) qout[19:16]<=1;

else

begin

qout[15:12]<=0;qout[19:16]<=qout[19:16]+1;

end

end

else

qout[15:12]<=qout[15:12]+1;

end

end

else

begin

if(outa==0)

begin

if(qout[3:0]==0)

begin

if([19:4]==0) qout[19:4]<=0;

else

begin

qout[19:4]<=qout[19:4]-1;qout[3:0]<=9;

end

end

else qout[3:0]<=qout[3:0]-1;

end

if(outa==1)

begin

if(qout[7:4]==0)

begin

if([19:8]==0) qout[19:8]<=0;

else

begin

qout[19:8]<=qout[19:8]-1;qout[7:4]<=9;

end

end

else qout[7:4]<=qout[7:4]-1;

end

if(outa==2)

begin

if(qout[11:8]==0)

begin

if([19:12]==0) qout[19:12]<=0;

else

begin

qout[19:12]<=qout[19:12]-1;qout[11:8]<=9;

end

end

else qout[11:8]<=qout[11:8]-1;

end

if(outa==3)

begin

if(qout[15:12]==0)

begin

if([19:16]==0) qout[19:16]<=0;

else

begin

qout[19:16]<=qout[19:16]-1;qout[15:12]<=9;

end

end

else qout[15:12]<=qout[15:12]-1;

end

end

end

end

always @(qout[19:0])

begin

case({qout[19:16],qout[15:12],qout[11:8],qout[7:4],qout[3:0]})

4'd0:{a,b,c,d,e,f,g}=7'b1111110;

4'd1:{a,b,c,d,e,f,g}=7'b0110000;

4'd2:{a,b,c,d,e,f,g}=7'b1101101;

4'd3:{a,b,c,d,e,f,g}=7'b1111001;

4'd4:{a,b,c,d,e,f,g}=7'b0110011;

4'd5:{a,b,c,d,e,f,g}=7'b1011011;

4'd6:{a,b,c,d,e,f,g}=7'b1011111;

4'd7:{a,b,c,d,e,f,g}=7'b1110000;

4'd8:{a,b,c,d,e,f,g}=7'b1111111;

4'd9:{a,b,c,d,e,f,g}=7'b1111011;

default:{a,b,c,d,e,f,g}=7'bx;

endcase

end

endmodule

`timescale 1ns/1ps

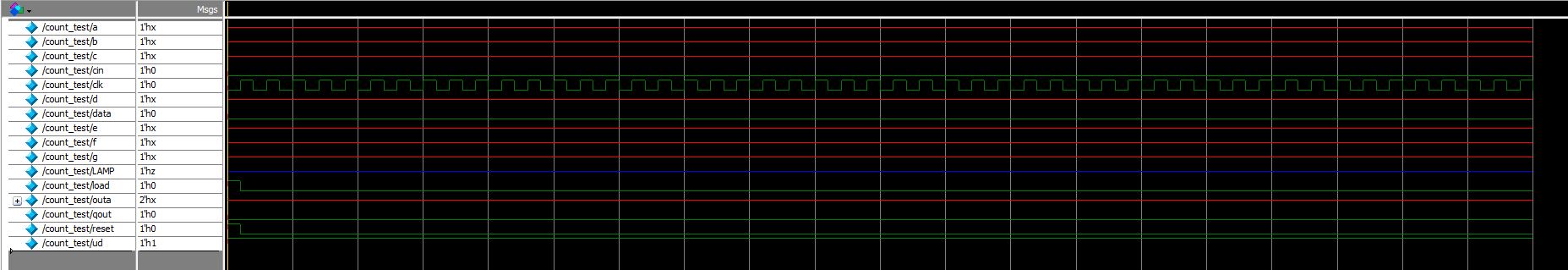

module count_test;

reg clk;

wire a,b,c,d,e,f,g;

wire[1:0] outa;

wire qout;

wire LAMP;

reg reset,load,cin,data,ud;

count count (clk,a,b,c,d,e,f,g,qout,reset,load,cin,data,ud);

initial begin

clk=1'b0;

reset=1'b1;

load=1'b1;

cin=1'b0;

data=1'b0;

ud=1'b1;

#10

reset=1'b0;

load=1'b0;

always

#20

clk=~clk;

count(

.clk(clk),

.reset(reset),

.load(load),

.data(data),

.cin(cin),

ud(ud),

);

end

endmodule

-- Compiling module count

** Error: C:/modeltech_10.1a/examples/count.v(12): Port mode is incompatible with declaration: load

** Error: C:/modeltech_10.1a/examples/count.v(14): Port mode is incompatible with declaration: cin

** Error: C:/modeltech_10.1a/examples/count.v(15): Port mode is incompatible with declaration: data

** Error: C:/modeltech_10.1a/examples/count.v(16): Port mode is incompatible with declaration: ud

** Error: C:/modeltech_10.1a/examples/count.v(30): near "=": syntax error, unexpected '=', expecting IDENTIFIER or TYPE_IDENTIFIER

** Error: C:/modeltech_10.1a/examples/count.v(31): near "=": syntax error, unexpected '=', expecting IDENTIFIER or TYPE_IDENTIFIER

** Error: C:/modeltech_10.1a/examples/count.v(32): near "=": syntax error, unexpected '=', expecting IDENTIFIER or TYPE_IDENTIFIER

** Error: C:/modeltech_10.1a/examples/count.v(33): near "=": syntax error, unexpected '=', expecting IDENTIFIER or TYPE_IDENTIFIER

** Error: C:/modeltech_10.1a/examples/count.v(34): near "=": syntax error, unexpected '=', expecting IDENTIFIER or TYPE_IDENTIFIER

** Error: C:/modeltech_10.1a/examples/count.v(104): near "[": syntax error, unexpected '['

** Error: C:/modeltech_10.1a/examples/count.v(116): near "[": syntax error, unexpected '['

** Error: C:/modeltech_10.1a/examples/count.v(128): near "[": syntax error, unexpected '['

** Error: C:/modeltech_10.1a/examples/count.v(140): near "[": syntax error, unexpected '['

** Error: C:/modeltech_10.1a/examples/count.v(146): near "[": syntax error, unexpected '[', expecting IDENTIFIER or TYPE_IDENTIFIER

-- Compiling module count_test

** Error: C:/modeltech_10.1a/examples/test.v(13): near "always": syntax error, unexpected always

** Error: C:/modeltech_10.1a/examples/test.v(17): Named argument not allowed in verilog.