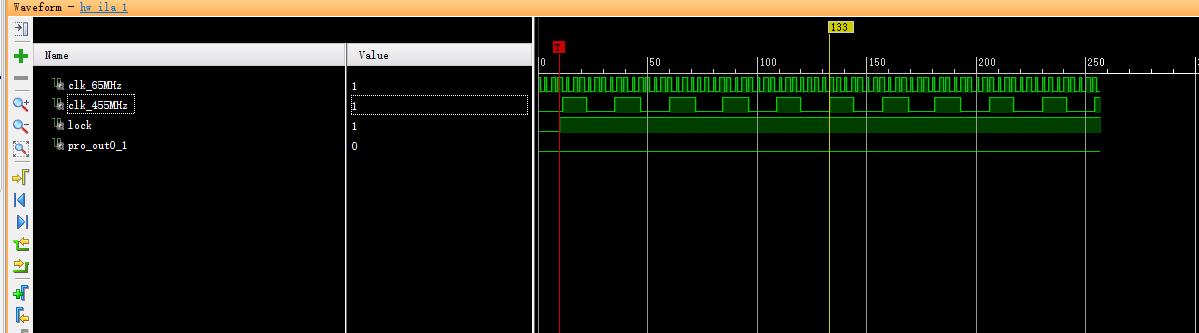

使用vivado进行观测PLL模块输出的时钟,发现正好顺序反了,不知道哪里有问题。

代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2016/09/28 15:04:30

// Design Name:

// Module Name: led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module led(

input sys_clk,

output reg [3:0] led

);

reg[31:0] timer_cnt;

(*mark_debug = "TRUE"*)wire clk_65MHz;

(*mark_debug = "TRUE"*)wire clk_455MHz;

(*mark_debug = "TRUE"*)wire lock;

(*mark_debug = "TRUE"*)wire pro_out0,pro_out1;//reset pll

//assign clk_in=sys_clk;

//主体部分

ila_1 m_ila(

.clk(sys_clk),

.probe0(clk_65MHz),

.probe1(clk_455MHz),

.probe2(pro_out0),

.probe3(lock)

);

clk_wiz_0 m_clk (

// Clock in ports

.clk_in1(sys_clk),

// Clock out ports

.clk_out1(clk_65MHz),

.clk_out2(clk_455MHz),

// Status and control signals

.reset(pro_out0),

.locked(lock)

);

vio_1 m_vio(

.clk(sys_clk),

.probe_in0(),

.probe_in1(),

.probe_out0(pro_out0),

.probe_out1(pro_out1)

);

always@(posedge sys_clk)

begin

if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule

就想知道为什么65MHz和455MHz顺序正好反了?