使用vivado编程verilog,遇到数组问题

问题描述:

我设置了reg型的数组

reg [23:0] rot[16:0] ;

reg [23:0] M [16:0] ;

这代表这17个24位的数据,接下来我在always中给他们赋值

rot[0] <= 24'd2949120;

rot[1] <= 24'd1740967;

rot[2] <= 24'd919879;

rot[3] <= 24'd466945;

rot[4] <= 24'd234378;

rot[5] <= 24'd117303;

rot[6] <= 24'd58666;

rot[7] <= 24'd29334;

rot[8] <= 24'd14667;

rot[9] <= 24'd7333;

rot[10] <= 24'd3667;

rot[11] <= 24'd1833;

rot[12] <= 24'd916;

rot[13] <= 24'd458;

rot[14] <= 24'd229;

rot[15] <= 24'd114;

rot[16] <= 24'd0;

rot[17] <= 24'd0;

M[0] <=24'b1000111100100001010011;

M[1] <=24'b0101000100110011110111;

M[2] <=24'b0010101001010010100100;

M[3] <=24'b0001010101100111000101;

M[4] <=24'b0000101010111011100001;

M[5] <=24'b0000010101011110110000;

M[6] <=24'b0000001010101111100000;

M[7] <=24'b0000000101010111110001;

M[8] <=24'b0000000010101011111000;

M[9] <=24'b0000000001010101111100;

M[10]<=24'b0000000000101010111110;

M[11]<=24'b0000000000010101011111;

M[12]<=24'b0000000000001010101111;

M[13]<=24'b0000000000000101010111;

M[14]<=24'b0000000000000010101011;

M[15]<=24'b0000000000000001010101;

M[16]<=24'b0000000000000000000001;

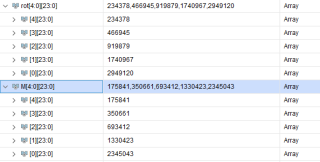

然后 在仿真的时候出现了这个

变成了只有5个24位的数据,这明显不对,导致后面结果不对。

是不是120位数组就是这个芯片的上限了?

我也尝试过使用wire型,assign赋值,结果也是这样