编码器的输入是并行的、128位的编码数据。(与串行检测器的输入信号x不同,这个是并行的)。在数字电路设计中,我们学过单点编码的编码器,即编码数据中只有一个点的位置需要编码。本题目需要检测多个点。这些点在128位中有如下特性:

- 在连续的16位当中 ,至多只有一个需要编码的点;

- 在总体的128位当中,有若干个(至多8点)需要编码的点;

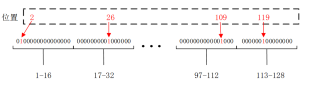

128位数据模式如下:

图1

完成多点编码器基本功能。要求设计一个多点编码器,对128位数据中需要编码的点进行编码,并且输出所有编码值的和,即2+26+…+109+119。

希望包括ASM图,Verilog代码以及测试文件testbench