各位大神,帮帮我吧,为什么vhdl代码仿真不出来操作码,定义了啊,难道是我操作的问题?求大神们帮帮我

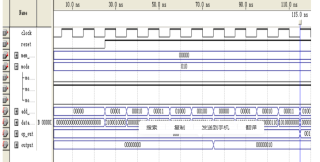

人家仿真出的结果

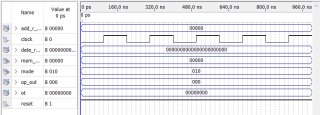

我仿真出来的结果

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

PACKAGE cpu_defs IS--定义程序包、包头、包体

TYPE opcode IS (load,sta,add,sub,and1,nop,jmp);

CONSTANT word_w: NATURAL :=8;

CONSTANT op_w: NATURAL :=3;

CONSTANT rfill: STD_LOGIC_VECTOR(op_w-1 downto 0):=(others =>'0');

FUNCTION op2slv(op:in opcode) RETURN STD_LOGIC_VECTOR;

END PACKAGE cpu_defs;

PACKAGE BODY cpu_defs IS

TYPE optable IS ARRAY(opcode) OF STD_LOGIC_VECTOR(op_w-1 DOWNTO 0);

CONSTANT trans_table:optable :=("000", "001", "010", "011", "100","101","110");

FUNCTION op2slv(op:IN opcode) RETURN STD_LOGIC_VECTOR IS

BEGIN

RETURN trans_table(op);

END FUNCTION op2slv;

function slv2op(slv:in std_logic_vector) return opcode is

variable transop:opcode;

begin

for i in opcode loop

if slv=trans_table(i) then

transop:=i;

end if;

end loop;

return transop;

end function slv2op;

END PACKAGE BODY cpu_defs;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL,IEEE.NUMERIC_STD.ALL;

USE ieee.cpu_defs.ALL;--使用自己定义的程序包

ENTITY CPU IS--实体说明

PORT(--端口说明

clock : IN STD_LOGIC;--时钟

reset : IN STD_LOGIC;--复位

mode : IN STD_LOGIC_VECTOR(2 DOWNTO 0);--查看用

mem_addr : IN UNSIGNED(word_w-op_w-1 DOWNTO 0);--地址

ot : OUT STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

data_r_out : OUT STD_LOGIC_VECTOR(21 DOWNTO 0);--微指令R

op_out : OUT STD_LOGIC_VECTOR(op_w-1 DOWNTO 0);--操作码

add_r_out : OUT UNSIGNED(4 DOWNTO 0)--微地址R

);

END ENTITY;

ARCHITECTURE rtl OF CPU IS--结构体

TYPE mem_array IS ARRAY (0 TO 2**(word_w-op_w)-1) OF STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);--定义RAM

SIGNAL mem : mem_array;

CONSTANT prog : mem_array:=(

0=> op2slv(load)&STD_LOGIC_VECTOR(TO_UNSIGNED(7,word_w-op_w)),

1=> op2slv(sta)&STD_LOGIC_VECTOR(TO_UNSIGNED(8,word_w-op_w)),

2=> op2slv(add)&STD_LOGIC_VECTOR(TO_UNSIGNED(9,word_w-op_w)),

3=> op2slv(sub)&STD_LOGIC_VECTOR(TO_UNSIGNED(10,word_w-op_w)),

4=> op2slv(and1)&STD_LOGIC_VECTOR(TO_UNSIGNED(11,word_w-op_w)),

5=> op2slv(nop)&STD_LOGIC_VECTOR(TO_UNSIGNED(12,word_w-op_w)),

6=> op2slv(jmp)&STD_LOGIC_VECTOR(TO_UNSIGNED(8,word_w-op_w)),

7=> STD_LOGIC_VECTOR(TO_UNSIGNED(2,word_w)),

8=> STD_LOGIC_VECTOR(TO_UNSIGNED(3,word_w)),

9=> STD_LOGIC_VECTOR(TO_UNSIGNED(4,word_w)),

10=> STD_LOGIC_VECTOR(TO_UNSIGNED(5,word_w)),

11=> STD_LOGIC_VECTOR(TO_UNSIGNED(6,word_w)),

OTHERS=>(OTHERS =>'0'));

TYPE microcode_array IS ARRAY (0 TO 17) OF STD_LOGIC_VECTOR(21 DOWNTO 0);

CONSTANT cod : microcode_array:=(--控制存储器

0=>"0000010100010000000001",

1=>"0000000000000110000010",

2=>"0000001010000000000011",

3=>"0000000100001000001111",

4=>"0000100010000000000000",

5=>"0000000000000100000000",

6=>"0000000010100001000000",

7=>"0000000010100000100000",

8=>"0000000000000110000100",

9=>"0101000001000000000101",

10=>"0000000000000110000110",

11=>"0000000000000110000111",

12=>"0000000000000110010000",

13=>"0000000000000000000000",

14=>"0000000000000110010001",

15=>"0000000000000000000000",

16=>"1000000010100000000000",

17=>"0010000010000000000000");

SIGNAL count : UNSIGNED(word_w-op_w-1 DOWNTO 0);

SIGNAL op : STD_LOGIC_VECTOR(op_w-1 DOWNTO 0);

SIGNAL z_flag : STD_LOGIC;

SIGNAL mdr_out : STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

SIGNAL mar_out : UNSIGNED(word_w-op_w-1 DOWNTO 0);

SIGNAL IR_out : STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

SIGNAL acc_out : UNSIGNED(word_w-1 DOWNTO 0);

SIGNAL sysbus_out : STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

BEGIN

PROCESS(reset,clock)

VARIABLE instr_reg : STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

VARIABLE acc : UNSIGNED(word_w-1 DOWNTO 0);

CONSTANT zero : UNSIGNED(word_w-1 DOWNTO 0):=(OTHERS =>'0');

VARIABLE mdr : STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

VARIABLE mar : UNSIGNED(word_w-op_w-1 DOWNTO 0);

VARIABLE sysbus : STD_LOGIC_VECTOR(word_w-1 DOWNTO 0);

VARIABLE microcode : microcode_array;

VARIABLE add_r : UNSIGNED(4 DOWNTO 0);

VARIABLE data_r : STD_LOGIC_VECTOR(21 DOWNTO 0);

VARIABLE temp : STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

IF reset='0'THEN

add_r:=(OTHERS=>'0');

count<=(OTHERS=>'0');

instr_reg:=(OTHERS=>'0');

acc:=(OTHERS=>'0');

mdr:=(OTHERS=>'0');

mar:=(OTHERS=>'0');

z_flag<='0';

mem<=prog;

sysbus:=(OTHERS=>'0');

ELSIF RISING_EDGE(clock)THEN

data_r:=microcode(TO_INTEGER(add_r));

IF data_r(4 DOWNTO 0)="01111"THEN --判断下地址

temp:="01"&op(2 DOWNTO 0);

add_r:=UNSIGNED(temp);

ELSE

add_r:=UNSIGNED(data_r(4 DOWNTO 0));

END IF;

data_r_out<=data_r;

add_r_out<=add_r;

--PC

IF data_r(16)='1'THEN--PC_bus='1'

sysbus:=rfill&STD_LOGIC_VECTOR(count);

END IF;

IF data_r(19)='1'THEN--load_PC='1'

count<=UNSIGNED(mdr(word_w-op_w-1 DOWNTO 0));

ELSIF data_r(10)='1'THEN--INC_PC='1'

count<=count+1;

ELSE

count<=count;

END IF;

--IR

IF data_r(15)='1'THEN--load_IR

instr_reg:=mdr;

END IF;

IF data_r(9)='1'THEN--Addr_bus='1'

sysbus:=rfill&instr_reg(word_w-op_w-1 DOWNTO 0);

END IF;

op<=instr_reg(word_w-1 DOWNTO word_w-op_w);

IR_out <= instr_reg;

op_out <=op;

--ALU

IF data_r(17)='1' THEN--load_ACC='1'

acc:=UNSIGNED(mdr);

END IF;

IF data_r(11)='1'THEN--ALU_ACC='1'

IF data_r(6)='1'THEN--ALU_add='1'

acc:=acc+UNSIGNED(mdr);

ELSIF data_r(5)='1'THEN--ALU_sub='1'

acc:=acc-UNSIGNED(mdr);

ELSIF data_r(20)='1' THEN--Transfer='1'

acc:=acc;

ELSIF data_r(21)='1'THEN--ALU_and1='1'

acc := acc and UNSIGNED(mdr);

END IF;

END IF;

IF data_r(18)='1'THEN--ACC_bus='1'

sysbus:=STD_LOGIC_VECTOR(acc);

END IF;

acc_out<=acc;

--RAM

IF data_r(14)='1'THEN--load_MAR='1'

mar:=UNSIGNED(sysbus(word_w-op_w-1 DOWNTO 0));

ELSIF data_r(12)='1'THEN--load_MDR='1'

mdr :=sysbus;

ELSIF data_r(8)='1'THEN--CS='1'

IF data_r(7)='1' THEN--R_NW='1'

mdr:=mem(TO_INTEGER(mar));

ELSE

mem(TO_INTEGER(mar))<=mdr;

END IF;

END IF;

IF data_r(13)='1'THEN--MDR_bus='1'

sysbus:=mdr;

END IF;

mdr_out<=mdr;

mar_out<=mar;

END IF;

sysbus_out<=sysbus;

END PROCESS;

PROCESS(mode,mem_addr)

BEGIN

--mode=0->sysbus

--mode=1->PC

--mode=2->result of ALU

--mode=3->IR

--mode=4->MAR

--mode=5->MDR

--mode=6->mem

ot<=(OTHERS =>'0');

CASE mode is

WHEN"000"=>

ot<=sysbus_out;

WHEN"001"=>

ot(word_w-op_w-1 DOWNTO 0)<=STD_LOGIC_VECTOR(count);

WHEN"010"=>

ot<=STD_LOGIC_VECTOR(acc_out);

WHEN"011"=>

ot<=IR_out;

WHEN"100"=>

ot(word_w-op_w-1 DOWNTO 0)<=STD_LOGIC_VECTOR(mar_out);

WHEN"101"=>

ot<=mdr_out;

WHEN"110"=>

ot<=mem(TO_INTEGER(mem_addr));

WHEN others=>

ot<=(OTHERS=>'Z');

END CASE;

END PROCESS;

END ARCHITECTURE;