如题,萌新要设计一个关于使用Basy3版来进行FPGA设计的小游戏

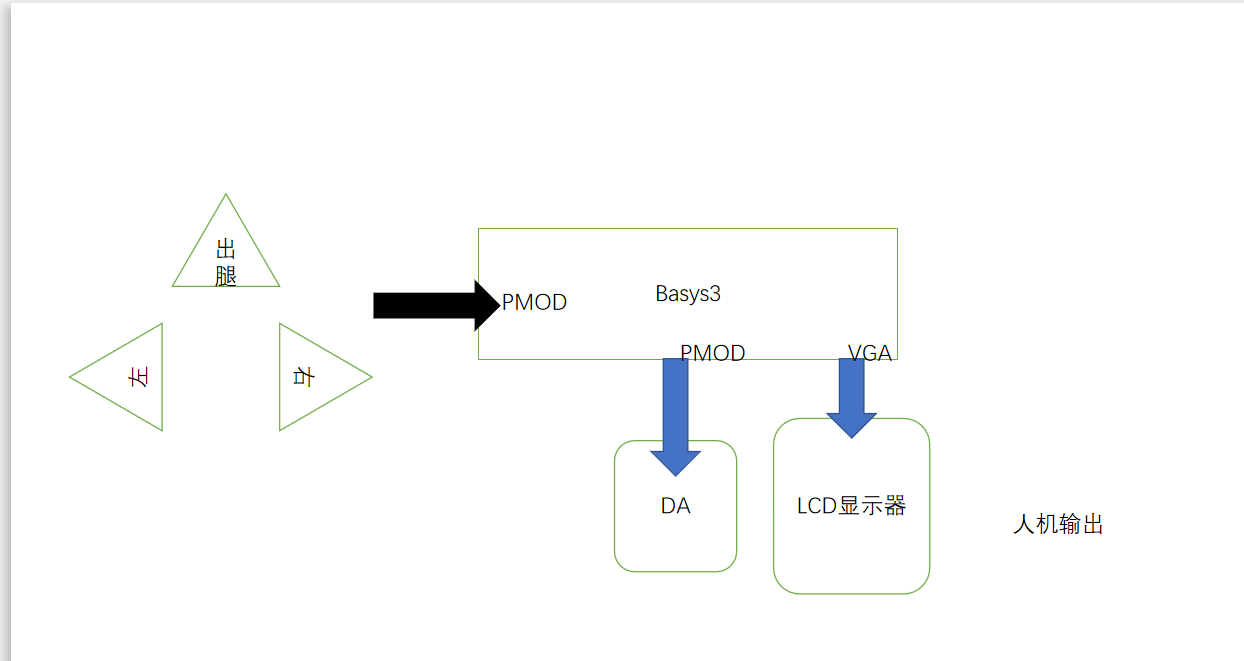

简易版暴力摩托,

主游戏界面上有3条道路,摩托车图标是一直往前开的,只需使用左右键控制使其变道,

撞击上小人的一瞬间,还有一个按键需触发,就是出腿,可以将小人单位消除,当然可以简化,

可以不使用出腿技能键,但最好还是有出腿技能键,

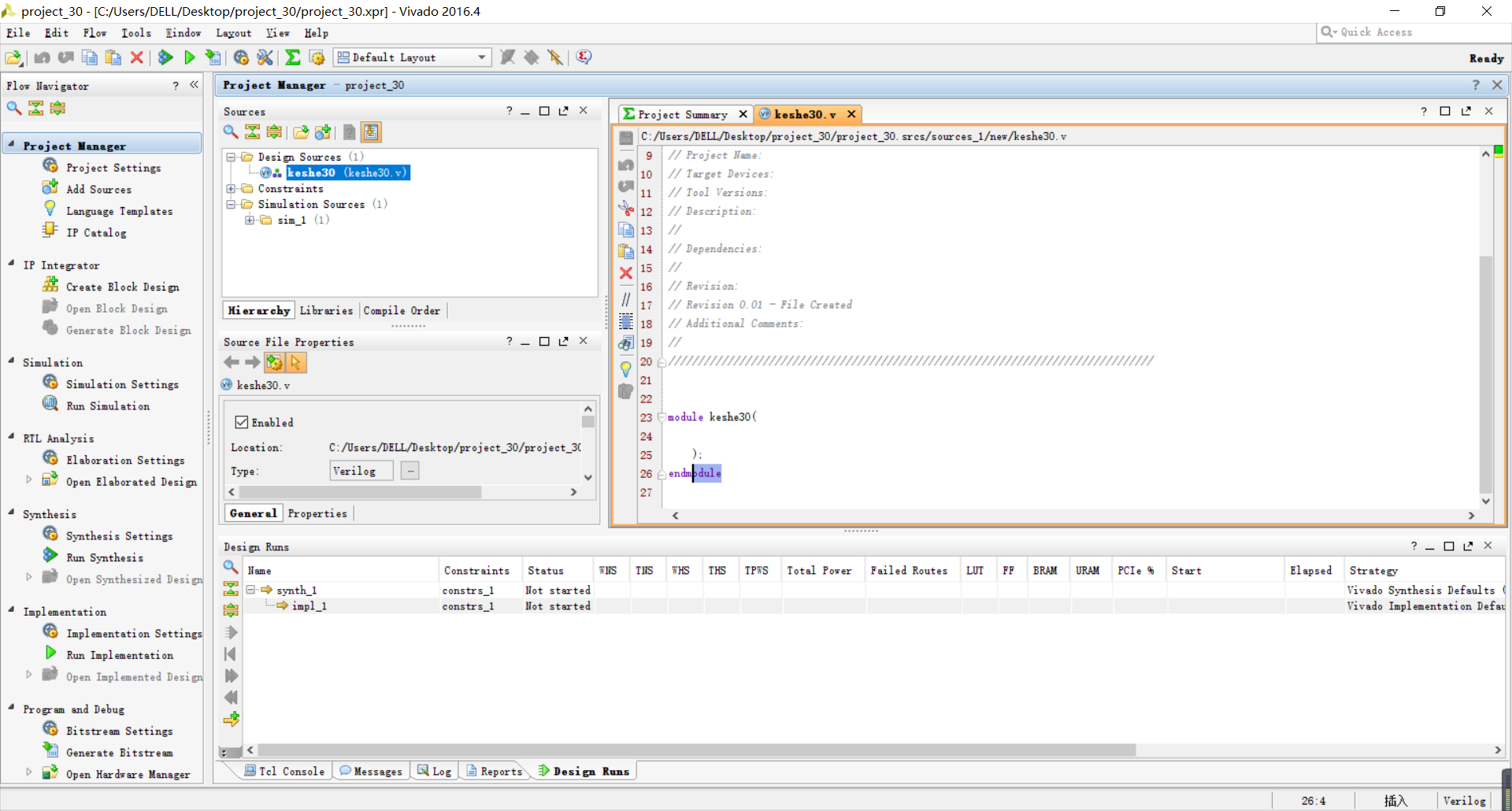

整体设计框架和示意图以及使用的烧录软件都在下面,

只想知道主要游戏代码如何设计,求大神帮助,问主现在是在校大学生一枚,能力实属有限..

关于使用Basy3板进行FPGA设计的小游戏

- 写回答

- 好问题 0 提建议

- 关注问题

- 邀请回答

-

1条回答 默认 最新

关注不知道你这个问题是否已经解决, 如果还没有解决的话:

关注不知道你这个问题是否已经解决, 如果还没有解决的话:- 你看下这篇博客吧, 应该有用👉 :FPGA极易入门教程----数码管篇(1)静态显示

如果你已经解决了该问题, 非常希望你能够分享一下解决方案, 以帮助更多的人 ^-^解决 无用评论 打赏 举报