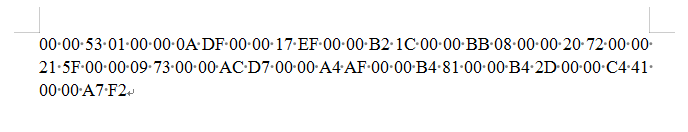

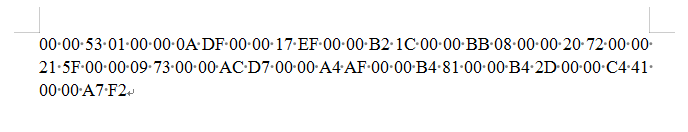

自己跑了一个别人的代码,通过串口传输到串口助手上。正常应该得到的数据是

如图这样14组计数值。

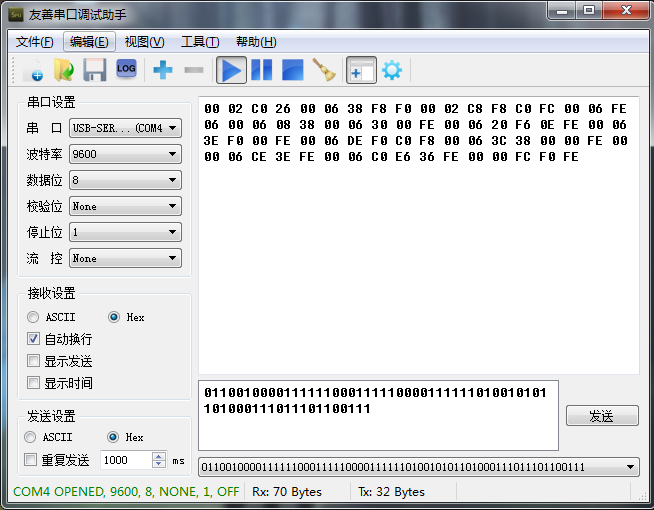

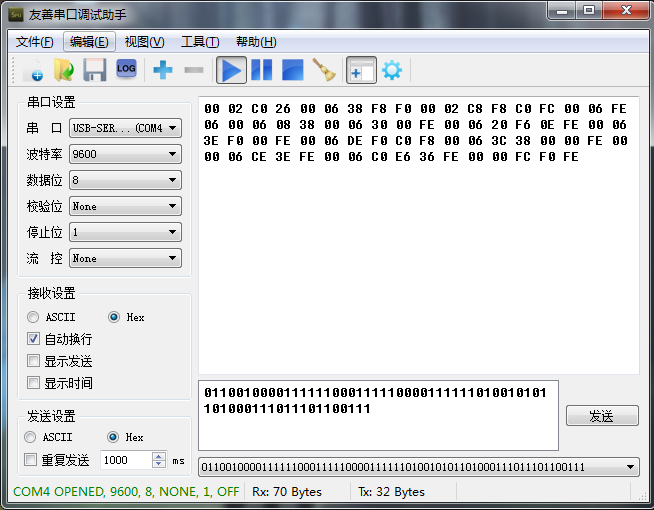

但我跑出的结果却是

如图这样毫无规律的计数值。并且每次收到的字节也可能不同。波特率我没有改过,程序也没有动过,不知道问题出现在哪,感觉不应该是因为不同的开发板导致的问题,还望大佬解答。

自己跑了一个别人的代码,通过串口传输到串口助手上。正常应该得到的数据是

如图这样14组计数值。

但我跑出的结果却是

如图这样毫无规律的计数值。并且每次收到的字节也可能不同。波特率我没有改过,程序也没有动过,不知道问题出现在哪,感觉不应该是因为不同的开发板导致的问题,还望大佬解答。