5.1

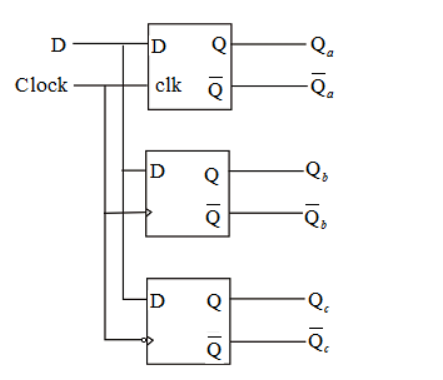

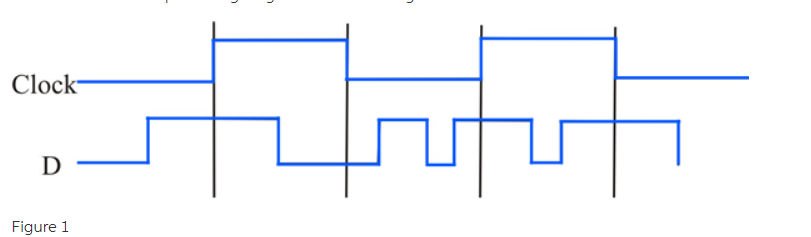

图1是电路,图2是clock与D的波形,请给出Qa,Qb,Qc的波形,并且要给出相应的verilog代码(源代码和仿真代码都要求)还要求有时序仿真截图

数字逻辑基础与verilog设计(加 斯蒂芬布朗)第三版习题答案(触发器,寄存器和计数器)

- 写回答

- 好问题 0 提建议

- 追加酬金

- 关注问题

- 邀请回答

-

1条回答 默认 最新

悬赏问题

- ¥15 kafka 分区副本增加会导致消息丢失或者不可用吗?

- ¥15 微信公众号自制会员卡没有收款渠道啊

- ¥15 stable diffusion

- ¥100 Jenkins自动化部署—悬赏100元

- ¥15 关于#python#的问题:求帮写python代码

- ¥20 MATLAB画图图形出现上下震荡的线条

- ¥15 关于#windows#的问题:怎么用WIN 11系统的电脑 克隆WIN NT3.51-4.0系统的硬盘

- ¥15 perl MISA分析p3_in脚本出错

- ¥15 k8s部署jupyterlab,jupyterlab保存不了文件

- ¥15 ubuntu虚拟机打包apk错误