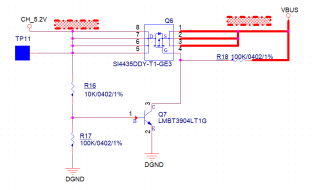

电路图如下:

设计的思想是,当CH_5.2V有5.2V电压时,Q7导通,Q6产生UGS压差,从而使Q6导通,VBUS处电压5.2V左右,当VBUS处有5V电压时,因Q6体二极管反向截止,理论上CH_5.2V处电压为0V

但在实际应用时,如果VBUS有5V电压时,CH_5.2V处也有5V的电压,并且Q7也处于导通状态,且在整个电路上,只有该地方使用了CH_5.2V网络,该5V电压不可能是由其他地方导致,实际与理论不同。而且通过Multisim仿真时,选择其他型号的mos管也存在这样的问题,是否是因为mos管漏电流过大,导致Q7导通,从而使Q6导通呢?请求各位解答。