1条回答 默认 最新

你知我知皆知 2024-08-10 02:44关注

你知我知皆知 2024-08-10 02:44关注以下回答参考 皆我百晓生、券券喵儿 等免费微信小程序相关内容作答,并由本人整理回复。

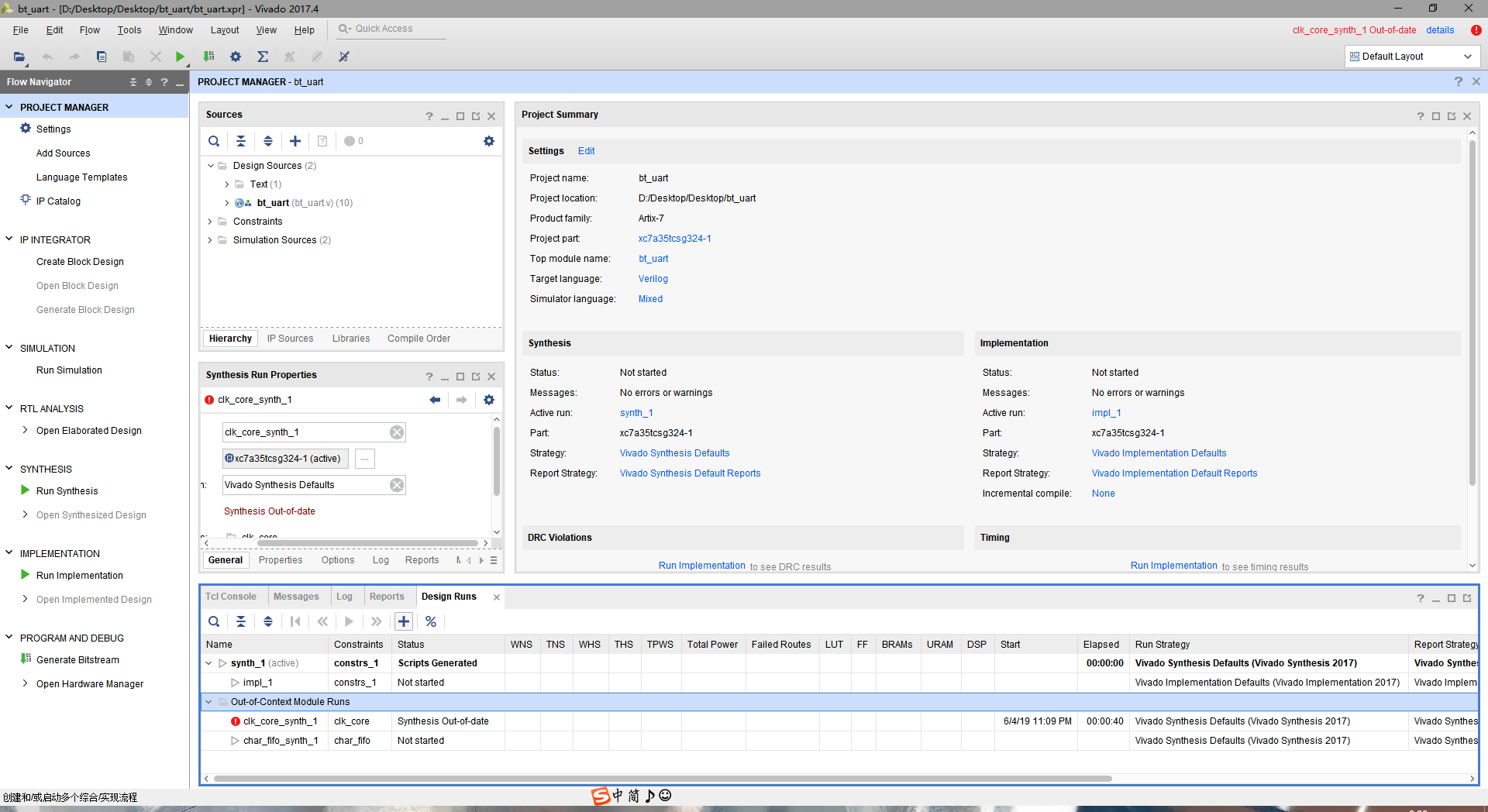

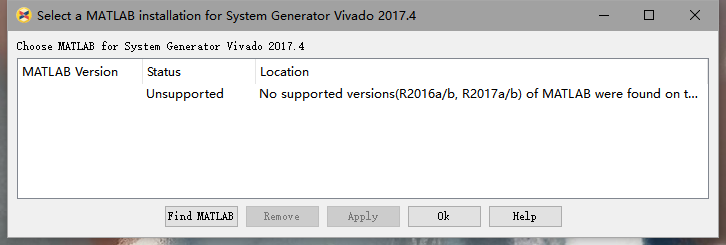

要解决这个问题,首先确保您已经正确安装了Vivado 2017.4,并且在您的计算机上已成功打开并运行系统生成器。接下来,请按照以下步骤操作:

- 确保您已安装了Vivado 2017.4。

- 打开Visual Studio Code(如果尚未安装)或其他支持Vivado编辑器的IDE。

- 在IDE中,导航到包含

D:/Desktop/Desktop/bt_uart/bt_uart.xpr文件夹的路径。 - 右键点击项目中的

bt_uart模块,然后选择“Open Source File”。将此文件拖放到IDE的编辑器中。 - 如果出现错误提示,尝试清除缓存或重新安装Visual Studio Code。

- 一旦导入成功,您可以开始使用Vivado来分析、设计和模拟IP核。

如果您仍然遇到问题,可能的原因包括:

- 您可能没有正确配置Vivado以处理特定的IP核类型。请查阅Vivado文档以了解如何配置和导入特定类型的IP核。

- 您可能没有正确设置编译选项或目标平台。检查您的编译命令以确保它们与您的环境相符。

- 可能存在DRC(验证规则检查)警告或错误,这些可能会导致合成过程失败。查看Vivado输出报告以了解详细信息,并根据指示进行调整。

- 可能存在时序冲突,例如不同信号之间的时钟依赖性不匹配。请检查相关约束和时序关系,确保所有依赖项都被满足。

- 可能存在逻辑错误,这些问题通常可以通过执行仿真或调试来发现。在Vivado中运行模拟以检测潜在的问题。

希望以上信息对您有所帮助!如有进一步问题,请随时提问。

解决 无用评论 打赏 举报