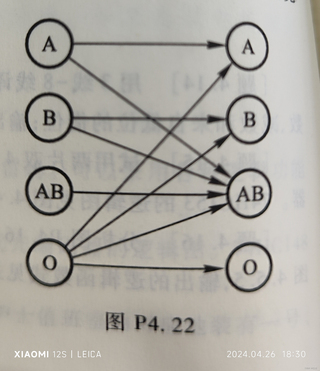

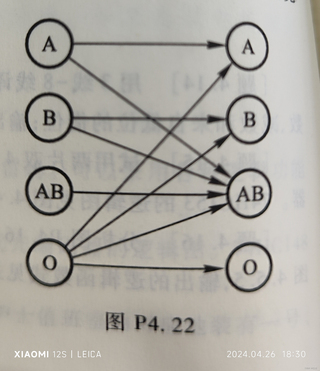

人的血型有A,B、AB、O四种。输血时输血者的血型与受血者血型必须符合图P4.22中用箭头指示的授受关系。试用3线-8线译码器设计一个逻辑电路,画出数据逻辑电路图,判断输血者与受血者的血型是否符合上述规定。(提示:可以用两个逻辑变量的四种取值表示输血者的血型,用另外两个逻辑变量的四种取值表示受血者的血型。)

人的血型有A,B、AB、O四种。输血时输血者的血型与受血者血型必须符合图P4.22中用箭头指示的授受关系。试用3线-8线译码器设计一个逻辑电路,画出数据逻辑电路图,判断输血者与受血者的血型是否符合上述规定。(提示:可以用两个逻辑变量的四种取值表示输血者的血型,用另外两个逻辑变量的四种取值表示受血者的血型。)

关注

关注引自免费微信小程序:皆我百晓生

为了设计这个逻辑电路,我们可以使用两个三输入二进制编码器分别表示输血者和受血者的血型。然后将编码后的输出进行比较,以确定它们之间的兼容性。这里我们将使用74HC138作为3线-8线译码器。

首先,我们定义输血者的血型为X1, X2, X3,受血者的血型为Y1, Y2, Y3。其中:

根据题目中的血型授受关系,我们需要检查以下情况是否成立:

我们将这些条件转换成逻辑表达式,并使用门电路(AND, OR, NOT)来实现。下面是逻辑电路的设计步骤:

以下是逻辑电路的详细描述:

首先,我们用74HC138译码器U1和U2分别解码输血者和受血者的血型。然后,我们将译码后的输出连接到逻辑门电路中,以检查输血者和受血者的血型是否匹配。匹配的条件如下:

逻辑门电路设计如下:

module blood_type_matcher(

input wire [2:0] donor_type, // 输血者血型(X1, X2, X3)

input wire [2:0] receiver_type, // 受血者血型(Y1, Y2, Y3)

output reg match // 输出匹配结果

);

// 译码器U1用于解码输血者血型

74HC138 U1 (

.I0(donor_type[0]),

.I1(donor_type[1]),

.I2(donor_type[2]),

.A(0), // 留空,因为我们只关心输出,不关心使能

.Y(0b0000_0000) // 初始化输出为0

);

// 译码器U2用于解码受血者血型

74HC138 U2 (

.I0(receiver_type[0]),

.I1(receiver_type[1]),

.I2(receiver_type[2]),

.A(0), // 留空,因为我们只关心输出,不关心使能

.Y(0b0000_0000) // 初始化输出为0

);

// 逻辑门电路以检查血型匹配

assign match = (donor_type == 3'b000 && (receiver_type == 3'b000 || receiver_type == 3'b100)) ||

(donor_type == 3'b001 && (receiver_type == 3'b001 || receiver_type == 3'b100)) ||

(donor_type == 3'b010 && (receiver_type == 3'b010 || receiver_type == 3'b100)) ||

(donor_type == 3'b011 && (receiver_type == 3'b000 || receiver_type == 3'b001 || receiver_type == 3'b010 || receiver_type == 3'b100));

endmodule

这个Verilog模块定义了一个名为blood_type_matcher的逻辑电路,它接受输血者和受血者的血型输入,并输出一个布尔信号match,表示两者是否匹配。

由于这是一个文本平台,无法绘制实际的电路图,但您可以参考上面的描述在纸上或使用电子设计自动化软件(如EAGLE, Proteus等)绘制电路图。这个电路由两个74HC138译码器和一些基本的门电路组成,如AND、OR和NOT门。