3、设计一个代码检测器,电路串行输入余3码,当输入非法数字时电路输出为0,否则输出为1.1)试作出状态图:2)进行化简:3)并利用D触发器进行电路设计。

3、设计一个代码检测器,电路串行输入余3码,当输入非法数字时电路输出为0,否则输出为1.1)试作出状态图:2)进行化简:3)并利用D触发器进行电路设计。

关注

关注让【道友老李】来帮你解答,本回答参考通义千问大模型编写,并整理提供,如果还有疑问可以点击头像关注私信或评论。

如果答案让您满意,请采纳、关注,非常感谢!### 问题描述 设计一个代码检测器,电路串行输入余3码,当输入非法数字时电路输出为0,否则输出为1。具体要求如下:

余3码是一种BCD码,其编码规则是将8421 BCD码的每一位加上3。合法的余3码范围是0011到1100(即十进制的0到9)。非法的余3码包括0000、0001、0010、1101、1110和1111。

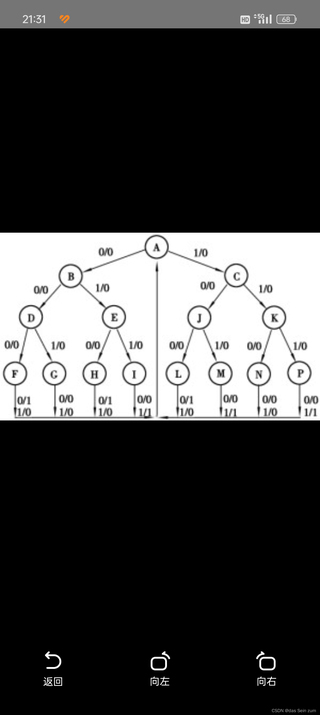

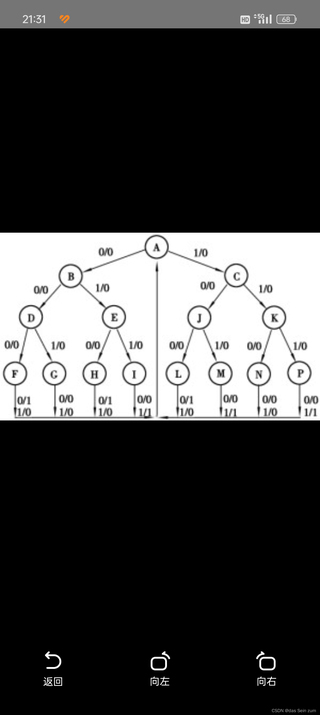

我们可以定义以下状态: - S0: 初始状态 - S1: 输入第一个比特 - S2: 输入第二个比特 - S3: 输入第三个比特 - S4: 输入第四个比特

状态转移图如下:

S0 --0/1--> S1

S1 --0/1--> S2

S2 --0/1--> S3

S3 --0/1--> S4

S4 --0/1--> S0 (输出0或1)

我们需要确定在每个状态下,输入哪些比特会导致非法余3码。根据余3码的定义,非法的余3码包括: - 0000 - 0001 - 0010 - 1101 - 1110 - 1111

我们可以列出状态表,并标记非法状态:

| 当前状态 | 输入 | 下一状态 | 输出 |

|---|---|---|---|

| S0 | 0 | S1 | - |

| S0 | 1 | S1 | - |

| S1 | 0 | S2 | - |

| S1 | 1 | S2 | - |

| S2 | 0 | S3 | - |

| S2 | 1 | S3 | - |

| S3 | 0 | S4 | - |

| S3 | 1 | S4 | - |

| S4 | 0 | S0 | 0 |

| S4 | 1 | S0 | 1 |

我们可以使用D触发器来实现这个状态机。D触发器的状态转移方程可以表示为: - D0 = S1 - D1 = S2 - D2 = S3 - D3 = S4

我们需要一个4位寄存器来存储当前状态。输出信号由S4决定。

module code_detector(

input clk,

input reset,

input in,

output reg out

);

reg [3:0] state;

always @(posedge clk or posedge reset) begin

if (reset) begin

state <= 4'b0000;

out <= 0;

end else begin

case (state)

4'b0000: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0001: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0010: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0011: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0100: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0101: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0110: begin

state <= {in, 3'b0};

out <= 0;

end

4'b0111: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1000: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1001: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1010: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1011: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1100: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1101: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1110: begin

state <= {in, 3'b0};

out <= 0;

end

4'b1111: begin

state <= {in, 3'b0};

out <= 0;

end

default: begin

state <= 4'b0000;

out <= 0;

end

endcase

end

end

endmodule

通过上述步骤,我们设计了一个能够检测非法余3码的电路。