我理解如果校验位比对失败的话应该不会进行译码吧,还请懂的朋友帮忙解惑

关注

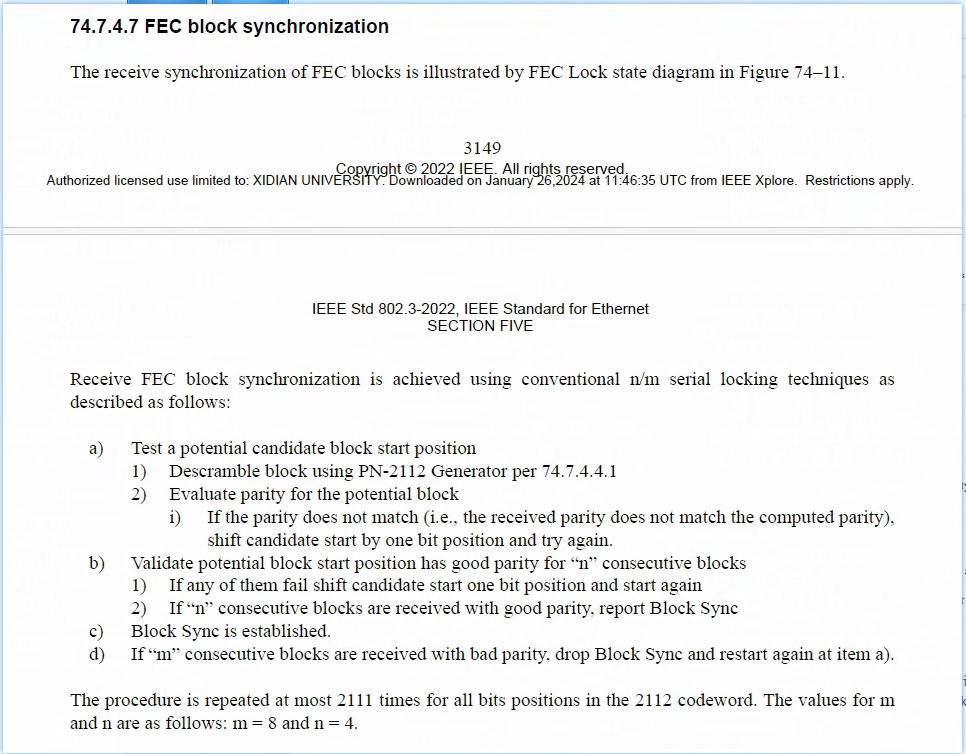

关注关于10G FEC(前向纠错)块同步的问题,您提到的校验位比对失败是否影响译码的疑问,这是一个涉及通信协议和纠错机制的典型问题。以下是详细解答:让【宝码香车】来帮你解答,本回答参考DeepSeek编写,并整理提供。

如果还有疑问可以点击头像关注私信或评论。如果答案让您满意,请采纳、点赞、关注,非常感谢!

FEC通过在传输数据中添加冗余校验位,使接收端能够检测和纠正一定数量的错误。常见于高速通信(如10G以太网、光通信等)。

“校验位比对失败是否跳过译码”取决于具体实现:

if (checksum_failed) {

discard_block();

return ERROR;

}

if verify_checksum() == FAILED:

corrected_data = fec_decode(received_block)

if is_valid(corrected_data):

accept_data()

如需进一步分析,请提供更多上下文(如协议规范或代码片段)。