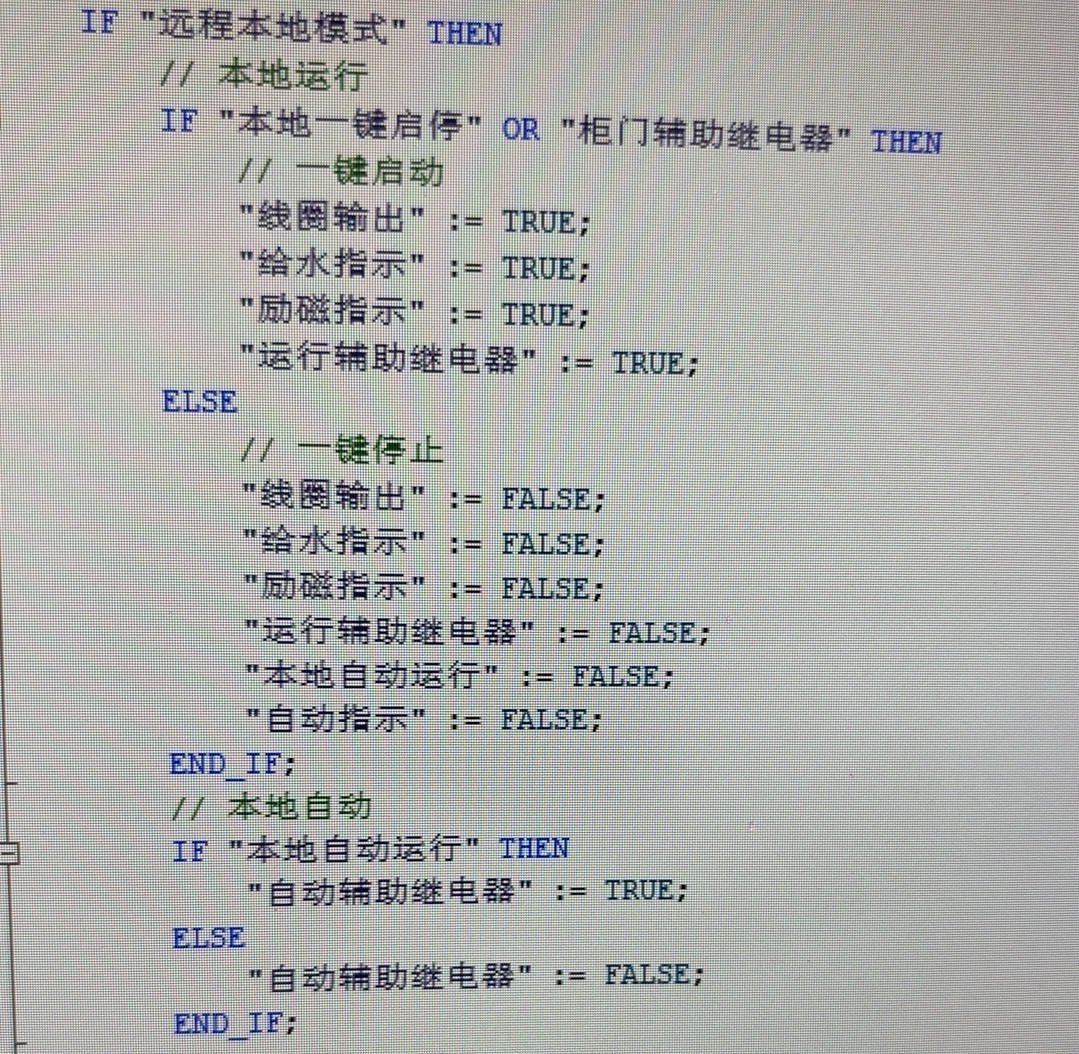

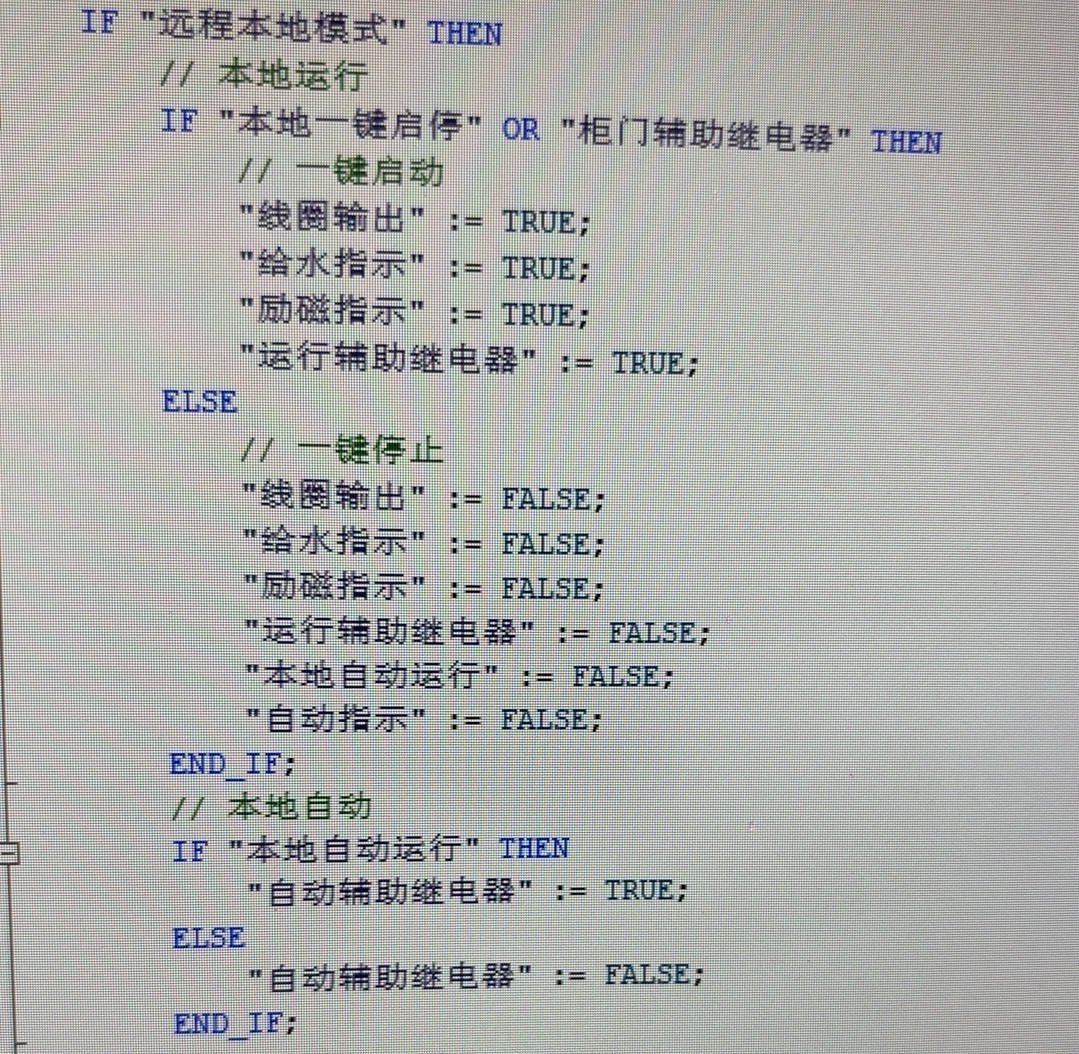

这段程序是SCL语言编写的,我现在想把他改成梯形图,但是试了加计数器和RS触发器效果不理想,有人可以解答下嘛,在线学习~

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

你好!我看到你遇到了问题,想将 SCL 语言编写的程序转换为梯形图,但是使用计数器和 RS 触发器没有达到预期的效果。

首先,SCL 语言是一种基于 VHDL 的 Hardware Description Language(HDL),用于描述数字电路的行为。梯形图是一种常见的数字电路图形,用于表示逻辑门的行为。

要将 SCL 语言编写的程序转换为梯形图,需要了解 SCL 语言的语法和 VHDL 的基本概念。下面是一些可能有用的建议:

以下是一个简单的示例代码,展示了如何使用 VHDL 语言将梯形图描述为 VHDL 代码:

library IEEE;

use IEEE.STD_LOGIC;

entity triangle_wave is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

output : out STD_LOGIC);

end triangle_wave;

architecture Behavioral of triangle_wave is

signal count : integer := 0;

begin

process(clk, rst)

begin

if rst = '1' then

count <= 0;

elsif rising_edge(clk) then

count <= count + 1;

end if;

end process;

output <= '1' when count < 3 else

'0' when count >= 3 and count < 6 else

'1';

end Behavioral;

这个示例代码描述了一个简单的梯形波形生成器,使用 VHDL 语言将梯形图描述为 VHDL 代码。

希望这些建议和示例代码能够帮助你解决问题。如果你需要更多帮助,请提供更多的信息和代码,我将尽力帮助你。