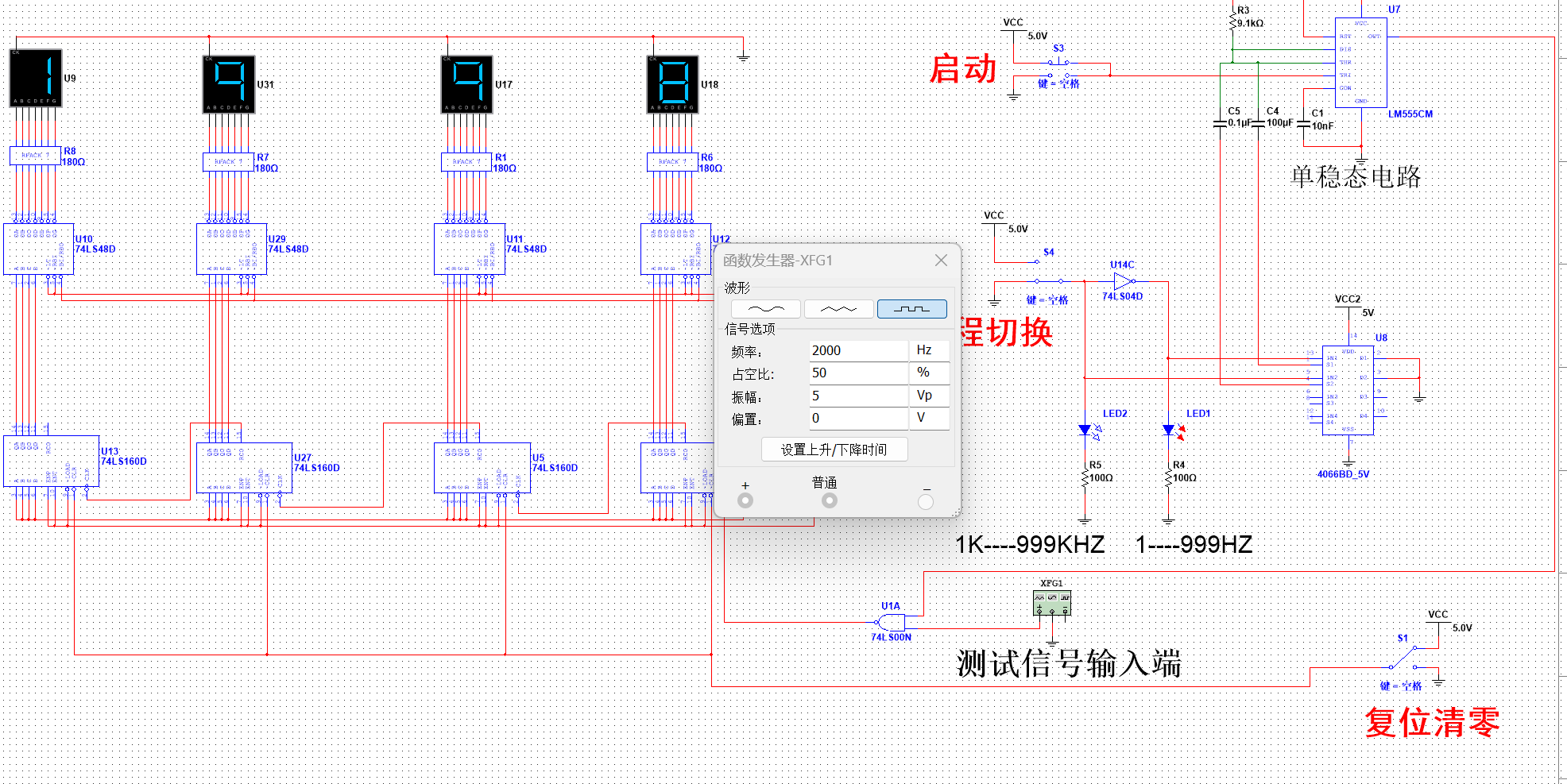

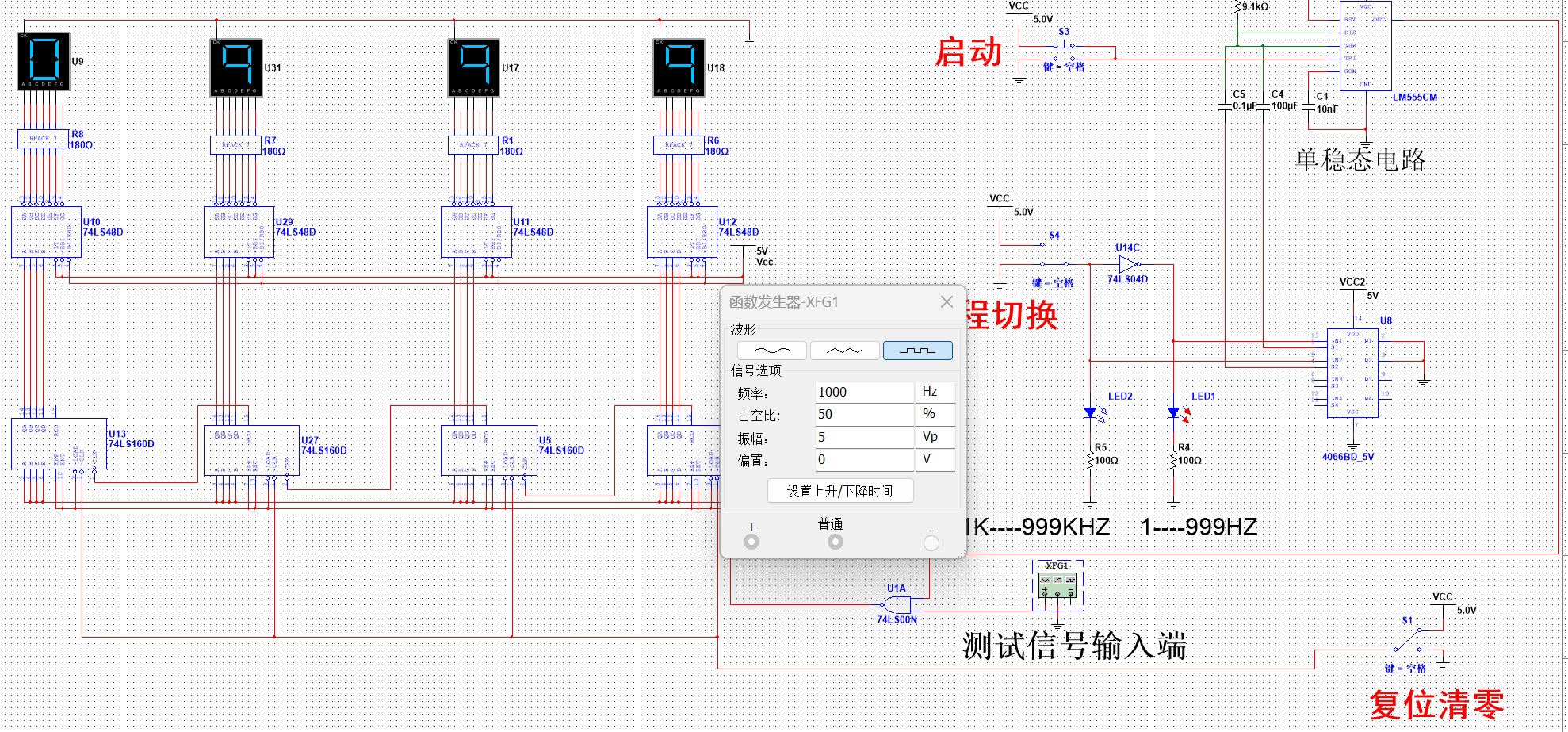

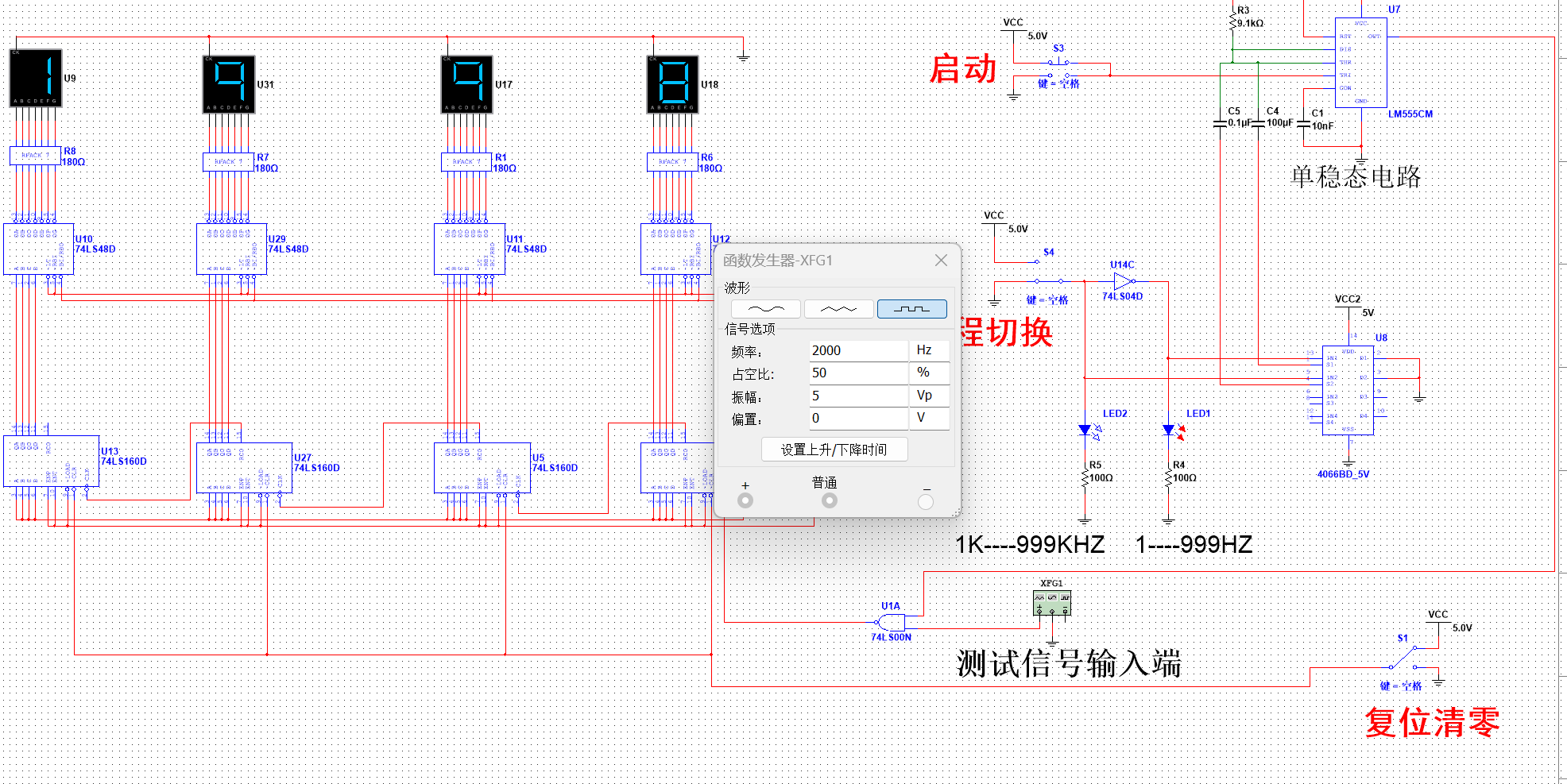

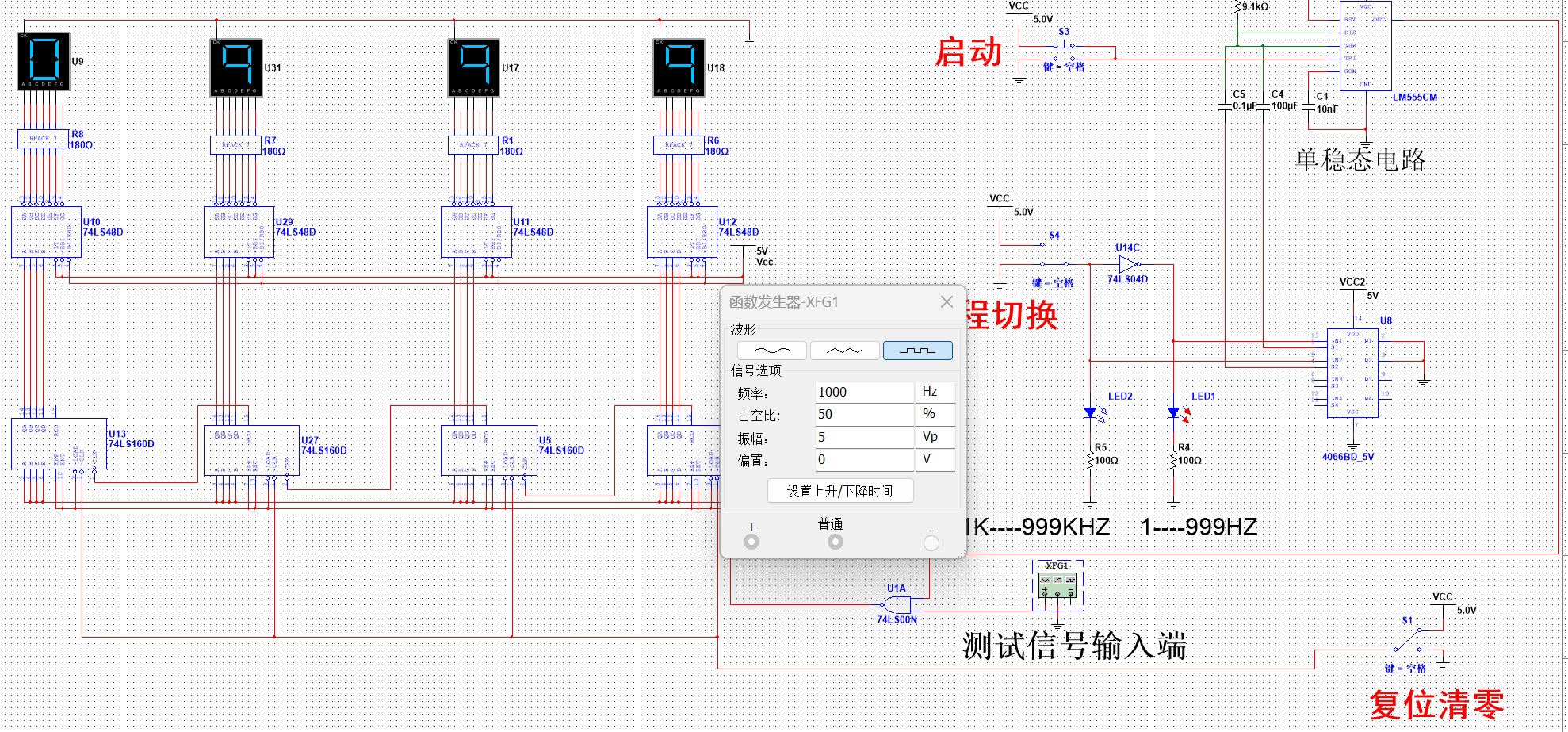

网上找了一个电路,是三位频率计,想四位频率计,然后就按他的方法续接了一个数码管,但输入1000Hz的时候,只显示999Hz,输入2000Hz,只显示1998Hz,这个问题怎么解决?求指点

网上找了一个电路,是三位频率计,想四位频率计,然后就按他的方法续接了一个数码管,但输入1000Hz的时候,只显示999Hz,输入2000Hz,只显示1998Hz,这个问题怎么解决?求指点

上午好☀️☀️☀️️

本答案参考通义千问

从你的描述来看,问题的核心在于数字频率计的计数器和分频器可能没有正确地处理输入信号的频率范围,导致显示的结果不准确。以下是一些可能的原因及对应的解决方案:

计数器溢出

1111100111),当输入频率超过这个值时,计数器会从头开始计数。分频器设计不合理

触发信号丢失

硬件限制

假设你正在使用Verilog编写计数器和分频器模块,以下是修改后的代码示例:

module frequency_counter(

input wire clk, // 系统时钟

input wire reset, // 复位信号

input wire signal_in, // 输入信号

output reg [11:0] count // 计数结果(四位十进制)

);

reg [31:0] counter; // 高精度计数器

reg signal_flag; // 触发信号标志

// 分频器:将输入信号分频到合适的范围

always @(posedge clk or posedge reset) begin

if (reset) begin

counter <= 0;

signal_flag <= 0;

end else begin

counter <= counter + 1;

if (counter == 100) begin // 分频比设置为100

counter <= 0;

signal_flag <= signal_in; // 捕获输入信号的上升沿

end

end

end

// 主计数器

always @(posedge clk or posedge reset) begin

if (reset) begin

count <= 0;

end else if (signal_flag) begin

count <= count + 1; // 每次检测到信号上升沿时计数+1

end

end

endmodule

通过以上分析和解决方案,你可以逐步排查问题并优化电路设计:

希望这些解决方案能帮助你解决问题!如果还有其他疑问,请随时补充说明。