前两问答案:2k8rom 1片 1k4位ram 2片

主要是电路没学过看不懂连线逻辑是什么

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

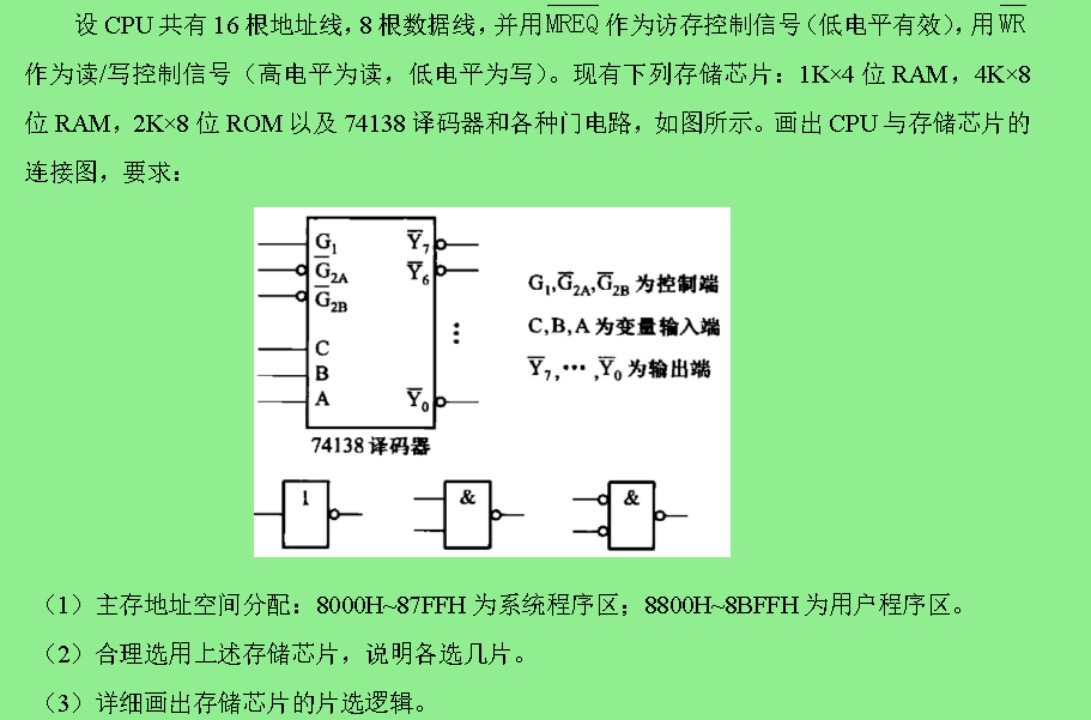

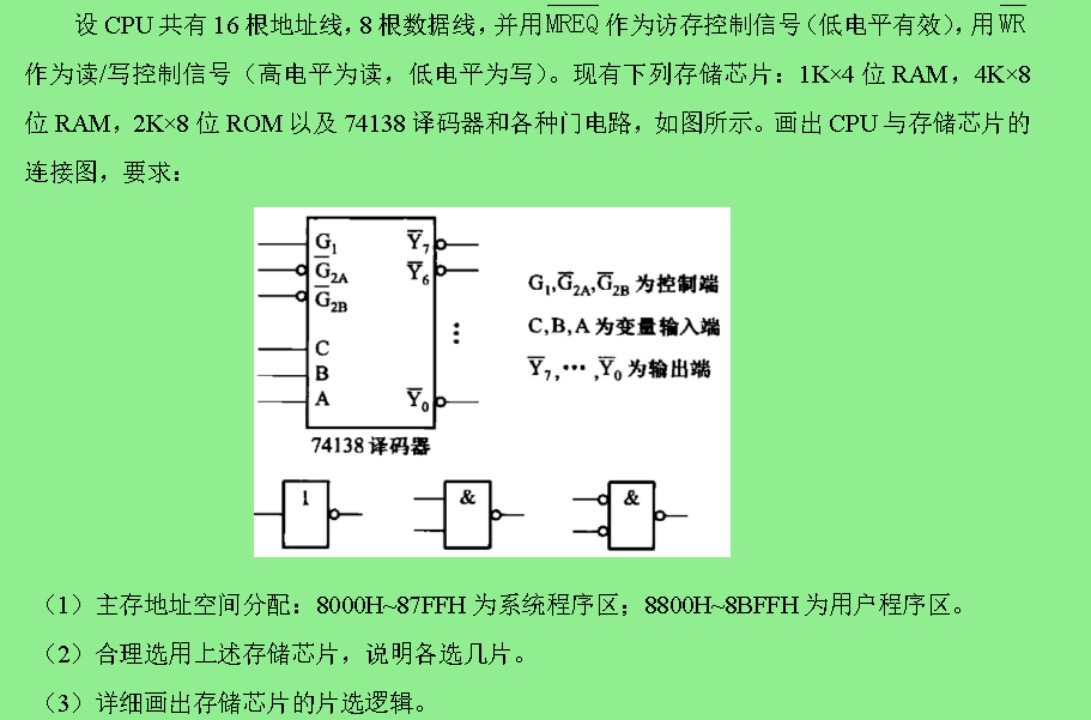

你遇到了一个硬件工程问题,关于 CPU 片选逻辑的电路设计。由于你没有学过数字电路,需要从基础知识开始解释。

CPU 片选逻辑是指 CPU 在多个片选中选择哪一个片作为当前执行的片。这个逻辑可以通过硬件电路实现。

下面是一个简单的 CPU 片选逻辑电路示意图:

graph LR

A[Address] -->|Address Bus|> B[Address Decoder]

B -->|Enable|> C[CPU 1]

B -->|Enable|> D[CPU 2]

B -->|Enable|> E[CPU 3]

C -->|Data Bus|> F[Memory]

D -->|Data Bus|> F[Memory]

E -->|Data Bus|> F[Memory]

在这个示意图中,Address Bus 将地址信号传递给 Address Decoder,Address Decoder 根据地址信号生成 Enable 信号, Enable 信号控制 CPU 的选择。 CPU 1、CPU 2 和 CPU 3 都可以通过 Enable 信号来选择是否执行。

在实际实现中,这个逻辑可以使用逻辑门(AND、OR、NOT 等)和 flip-flop(FF)等基本电路元件来实现。

如果你想深入了解 CPU 片选逻辑的电路设计,可以查看相关的数字电路教程和书籍,或者实践一些简单的电路设计项目。

希望这些建议能够帮助你更好地理解 CPU 片选逻辑的电路设计。