让 “紫雾凌寒” 来帮你回答,本回答结合 DeepSeek

如果还有问题,请评论或点击头像私信,如果有帮助到您, 请关注、采纳、点赞

- 关键点分析:

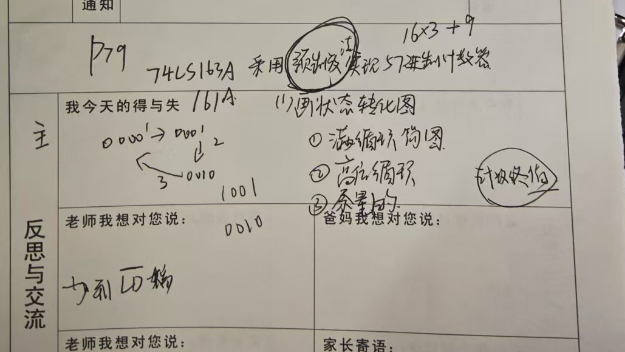

- 要使用74LS163A芯片通过预置法实现57进制计数器。需要了解74LS163A芯片的功能,它是同步4位二进制计数器,有清零(CLR)、预置(LOAD)、计数(CTP、CTT)等功能引脚。

- 确定预置值,57进制计数器意味着计到57后重置。

- 设计合适的电路连接和逻辑控制来实现计数和预置功能。 - 解决方案:

- 74LS163A引脚功能:- CLR:清零引脚,低电平有效。

- LOAD:预置引脚,低电平有效。

- CTP、CTT:计数使能引脚,高电平有效。

- D0 - D3:数据输入引脚。

- Q0 - Q3:数据输出引脚。

- TC:计数溢出信号,当计数到最大值(15)时输出高电平。

- 计算预置值:

- 57进制计数器,需要预置的值为57的二进制表示。57转换为二进制是0011 1001。

- 电路连接:

- 将CLR引脚接高电平,保证正常计数,不意外清零。

- 将LOAD引脚接低电平实现预置功能。

- 将D0 - D3分别接0、0、1、1、1、0、0、1。

- CTP和CTT接高电平使能计数。

- 当计数器计到56(二进制0011 1000)时,TC输出高电平,通过逻辑电路反馈到LOAD引脚,使其变为低电平,在下一个时钟上升沿时进行预置,重新从57开始计数。

- 示例逻辑图:

- 用一个简单的与非门电路来实现反馈逻辑。将74LS163A的TC引脚连接到一个与非门的输入,与非门的输出连接到74LS163A的LOAD引脚。当TC为高电平时,与非门输出低电平,实现预置功能。

- 这里用文字描述难以准确画出标准逻辑图,你可以通过专业的电路设计软件(如Altium Designer等)来绘制具体的电路图。大致如下:

- 74LS163A的VCC接电源,GND接地。

- CLR接高电平(如接 +5V)。

- LOAD通过与非门接低电平(当TC为高时)。

- D0 - D3分别接相应电平(0、0、1、1、1、0、0、1)。

- CTP和CTT接高电平(如 +5V)。

- Q0 - Q3连接到需要显示或进一步处理的地方。

- 多种解决方案优缺点:

- 方案一:上述直接利用74LS163A的预置和计数功能结合简单逻辑电路实现。- 优点:电路结构相对简单,易于理解和实现,成本较低。

- 缺点:对于复杂的逻辑需求扩展能力有限,如果要改变计数进制等参数,可能需要重新设计部分逻辑电路。

- 方案二:使用可编程逻辑器件(PLD),如FPGA。

- 优点:可以通过编程灵活实现各种进制计数器,修改方便,可扩展性强。

- 缺点:需要一定的编程基础和开发工具,成本相对较高,开发周期可能较长。

- 总结:

- 用74LS163A采用预置法实现57进制计数器,关键在于正确连接引脚和设计反馈逻辑来实现预置和计数功能转换。通过合理的电路连接和逻辑控制,能够满足57进制计数的要求。不同实现方案各有优缺点,可根据实际需求选择合适的方法。

希望以上解答能帮助你理解和实现该57进制计数器。如果还有其他疑问,欢迎继续提问。

希望以上解答对您有所帮助。如果您有任何疑问,欢迎在评论区提出。

关注

关注