图当中我用verilog-A代码写了一个4bit的flash ADC和一个理想DAC,所有设置和仿真结果如上图,我现在想知道、INL和DNL两个函数应该如何设置,以及每个选项的具体意义。

图当中我用verilog-A代码写了一个4bit的flash ADC和一个理想DAC,所有设置和仿真结果如上图,我现在想知道、INL和DNL两个函数应该如何设置,以及每个选项的具体意义。

关注

关注让【宝码香车】来帮你解答,本回答参考DeepSeek编写,并整理提供。

如果还有疑问可以点击头像关注私信或评论。如果答案让您满意,请采纳、点赞、关注,非常感谢!

若您愿意支持,欢迎直接打赏,将不胜感激!

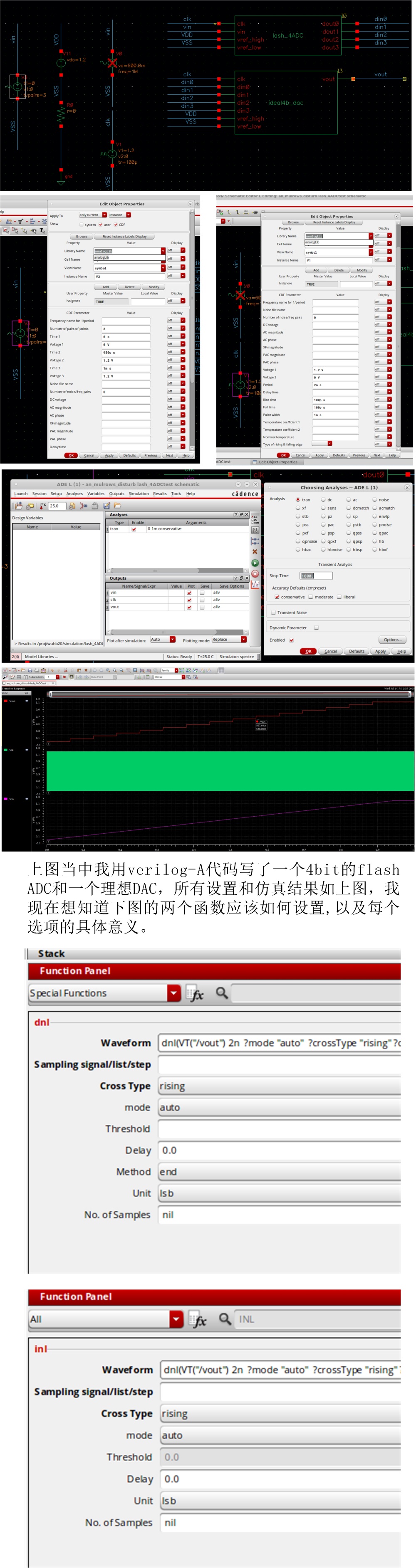

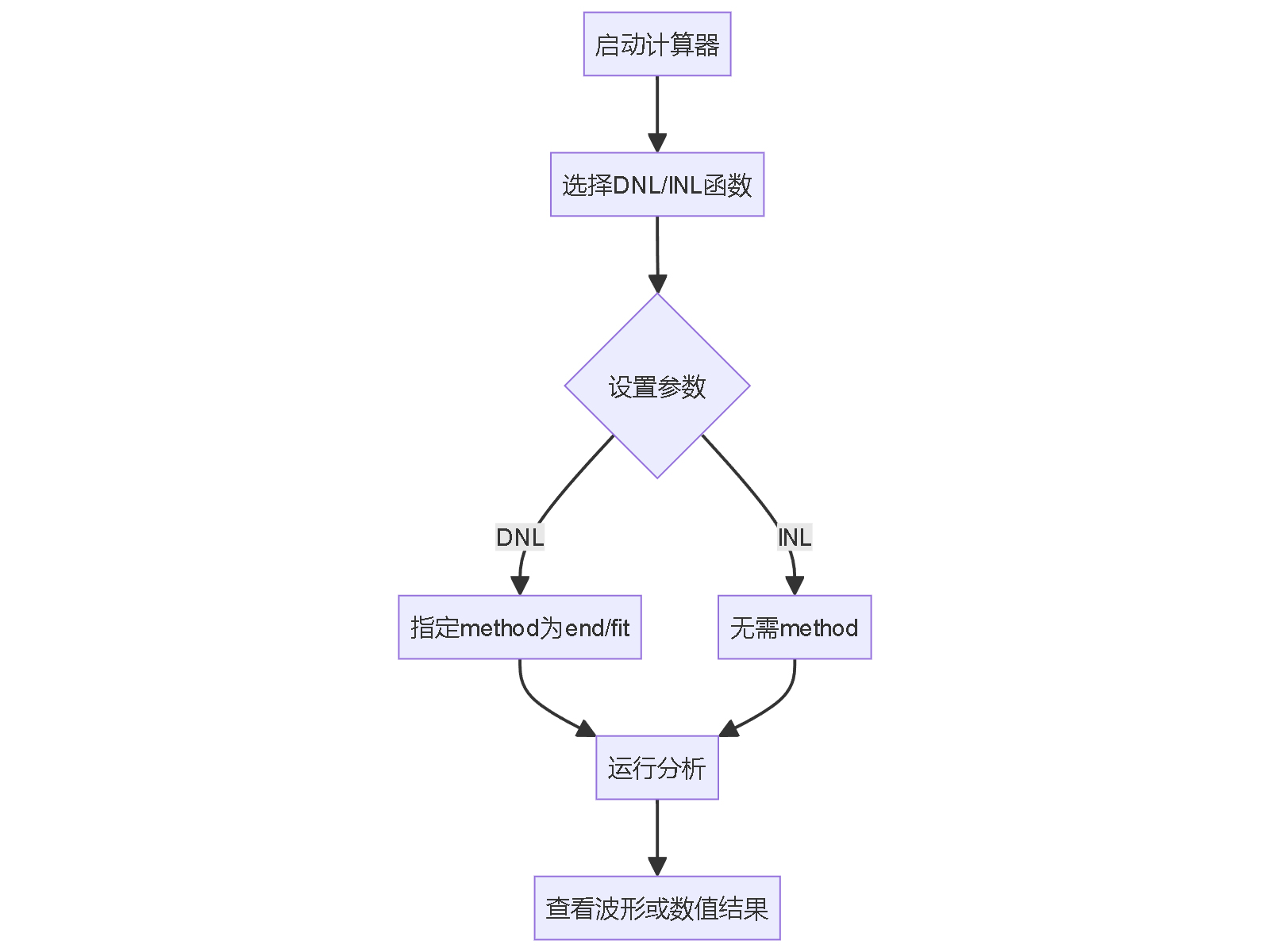

在Cadence Virtuoso计算器中,DNL(差分非线性)和INL(积分非线性)是ADC性能分析的重要函数。以下是具体设置和选项说明:

dni(VT("/vout") 2n ?mode "auto" ?crossType "rising" ?threshold 0.5 ?delay 0.0 ?method "end" ?unit "lsb" ?noSamples nil)

VT("/vout"))。2n表示2mV,假设1LSB=2mV)。rising:在上升沿采样。falling:在下降沿采样。auto:自动检测转换点。manual:手动指定阈值。0.0表示无延迟)。end:使用最后一个采样点计算DNL。fit:通过拟合曲线计算。lsb:结果以LSB为单位。volt:结果以电压为单位。nil表示自动选择)。inl(VT("/vout") 2n ?mode "auto" ?crossType "rising" ?threshold 0.5 ?delay 0.0 ?unit "lsb" ?noSamples nil)

method)。method参数)。

noSamples或threshold。如有进一步问题,建议提供仿真波形截图以便更精准分析。