让 “紫雾凌寒” 来帮你回答,本回答结合 DeepSeek

如果还有问题,请评论或点击头像私信,如果有帮助到您, 请关注、采纳、点赞

- 关键点分析:

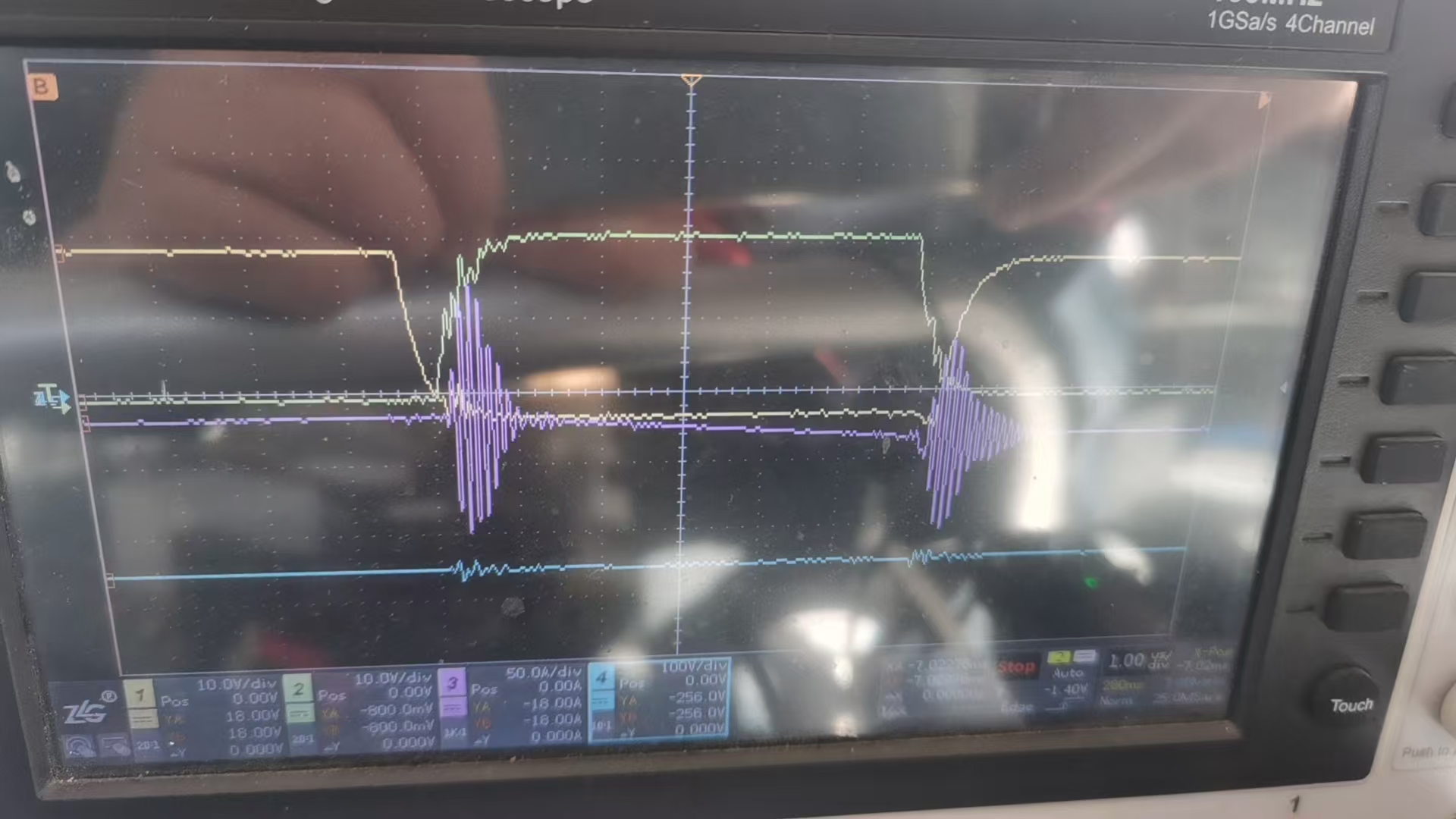

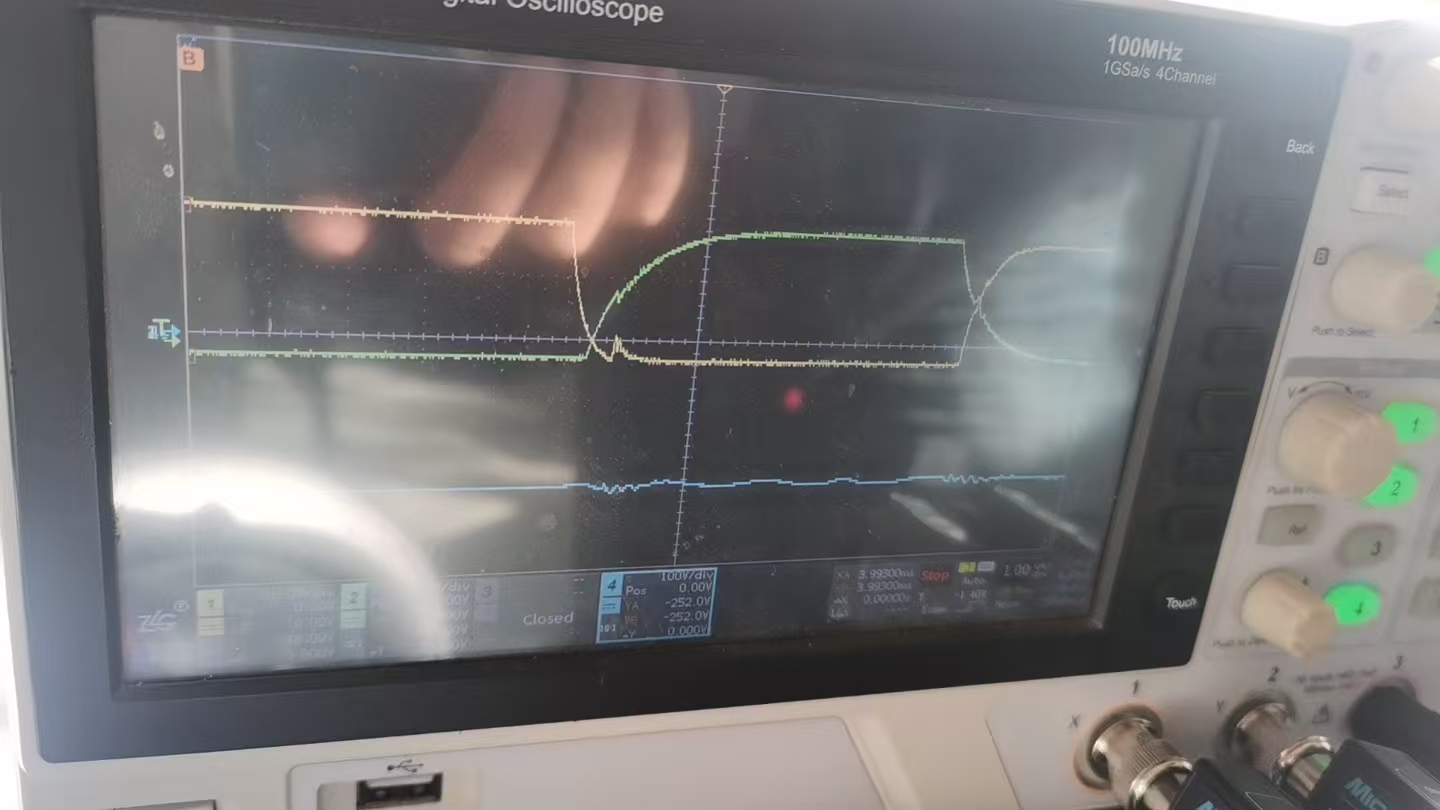

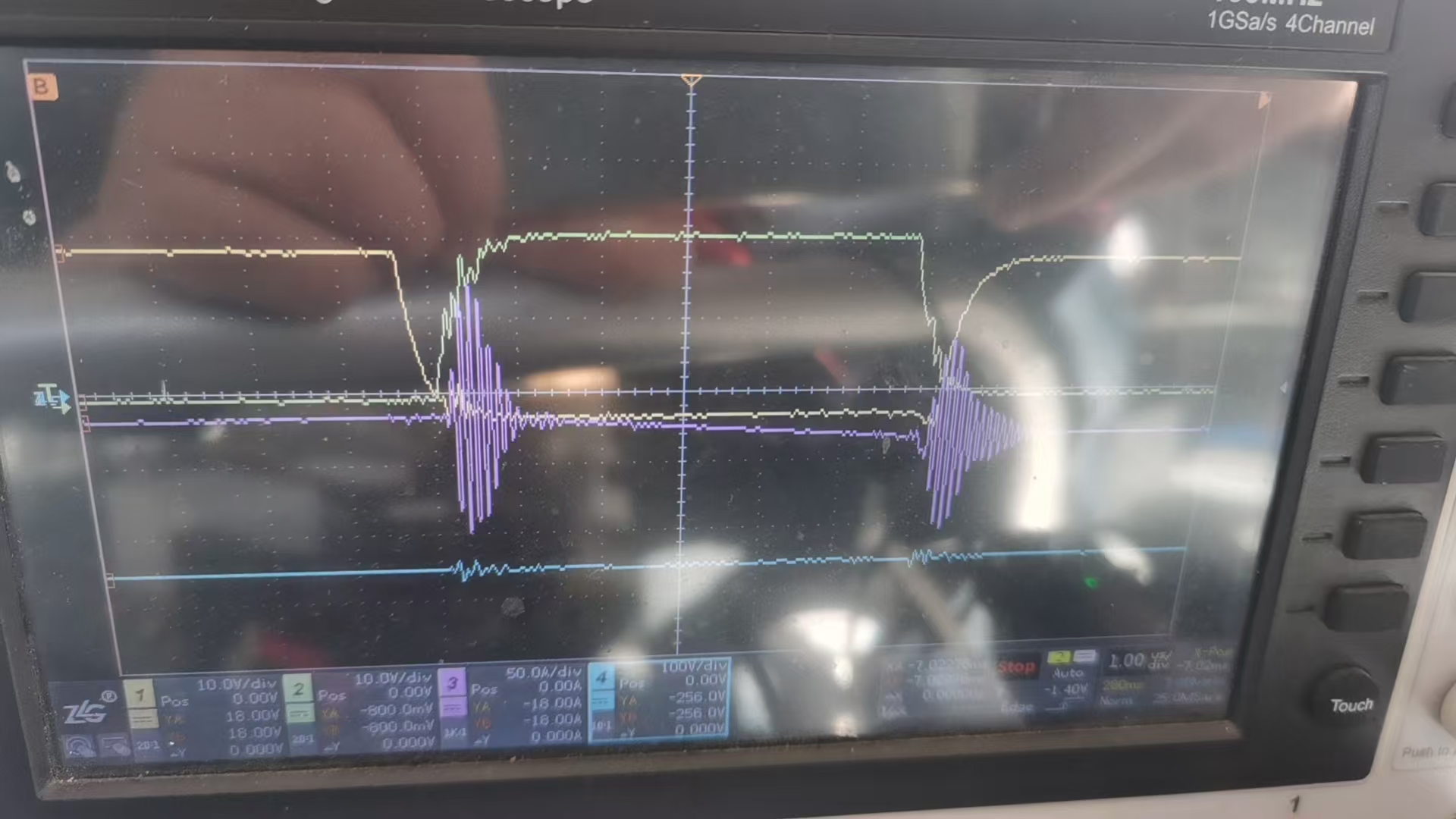

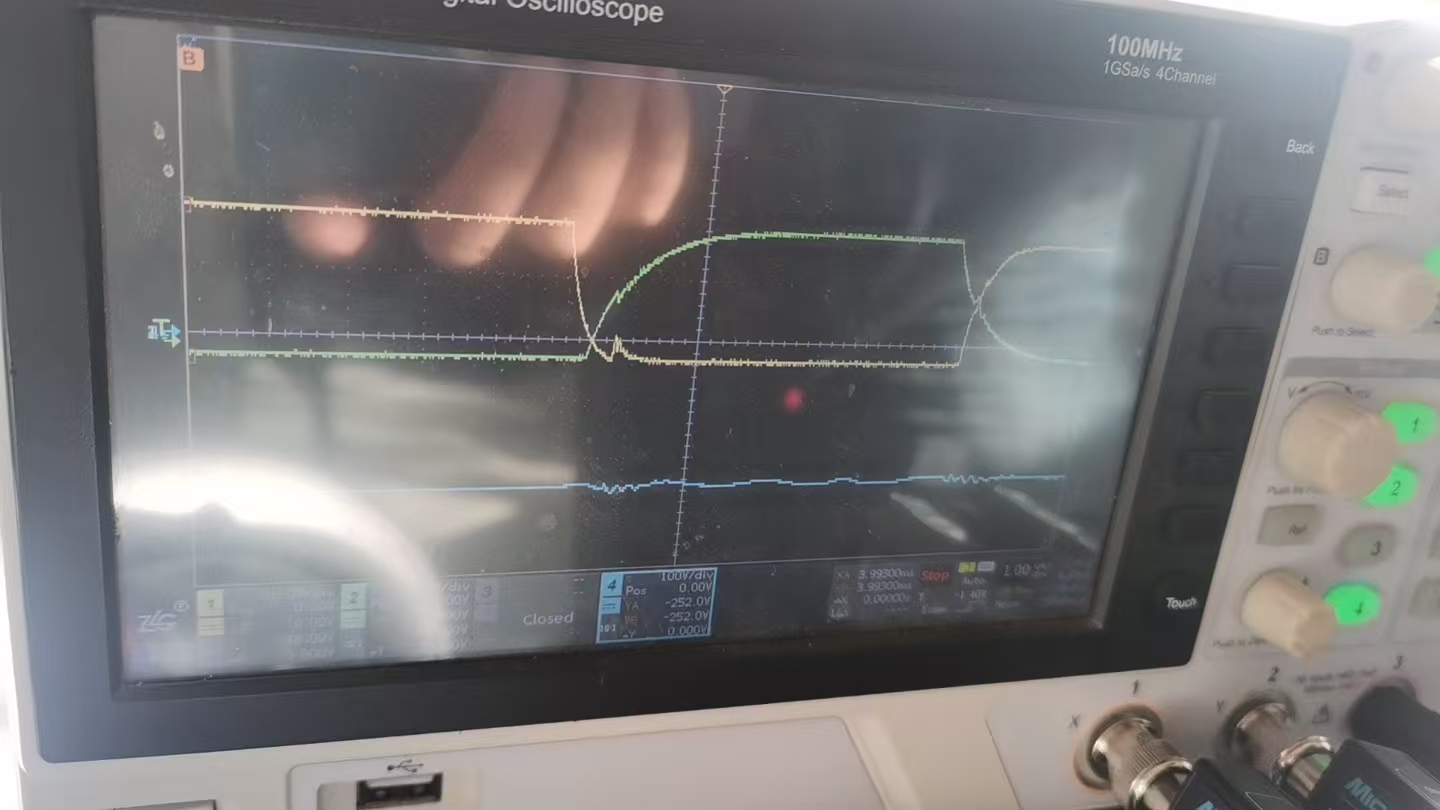

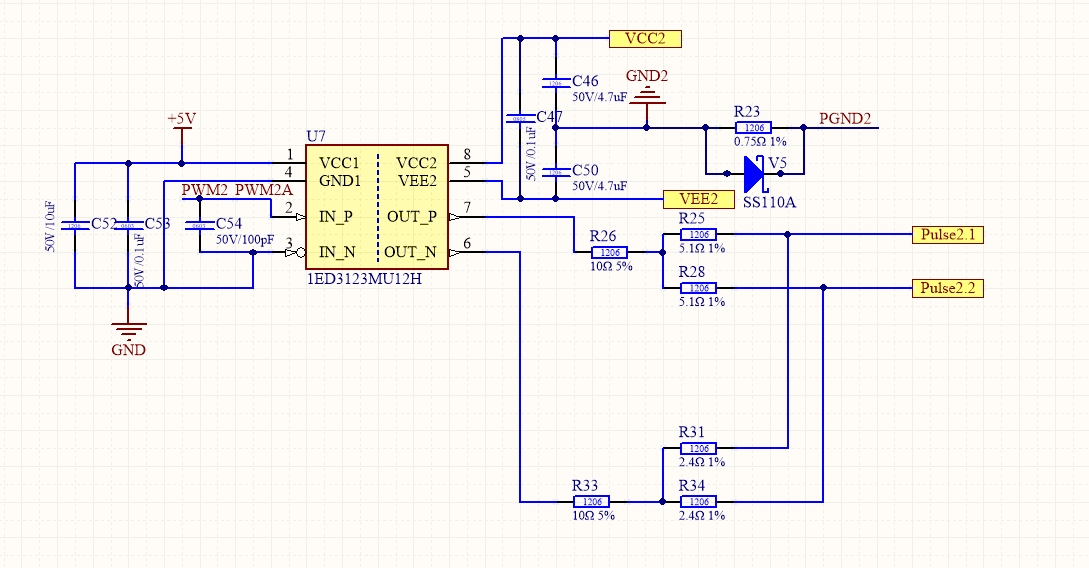

- 问题核心在于boost升压电路中MOS管驱动信号上升沿和下降沿过缓且有振荡,导致电感电流波动大。

- 探讨了在DS之间并联电容这一措施对振荡和驱动信号的影响,即抑制振荡但加剧驱动信号过缓及增大损耗。 - 可能导致驱动信号过缓及振荡的原因及解决方法:

- 原因:- 寄生电感:电路中的布线电感、MOS管引脚电感等寄生电感会影响信号的快速变化。当驱动信号上升或下降时,寄生电感会阻碍电流的快速变化,导致信号过缓。例如,若布线不合理,走线过长,寄生电感就会增大。

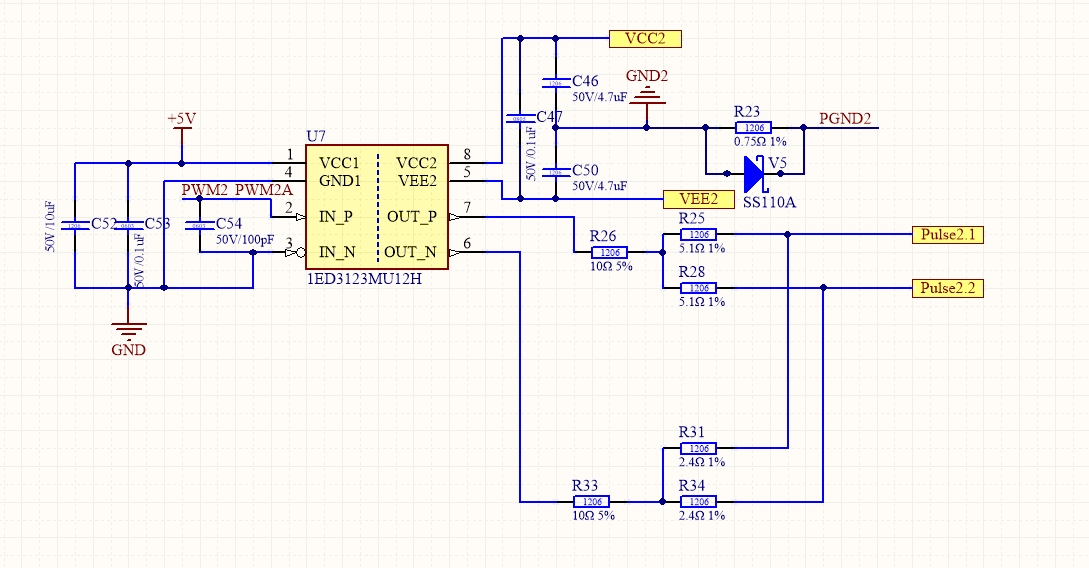

- 驱动能力不足:驱动电路的输出电流或电压不够,无法快速地使MOS管开通或关断。比如驱动芯片的选型不当,其输出能力无法满足MOS管的需求。

- MOS管的输入电容:MOS管自身的输入电容较大,在驱动信号上升和下降时,需要对其进行充电和放电,这会消耗一定时间,导致信号过缓。

- 解决方法:

- 优化布线:尽量缩短布线长度,减少寄生电感。例如,将MOS管的驱动引脚与电源引脚尽量靠近,减小走线长度。

- 增强驱动能力:更换驱动能力更强的驱动芯片。比如选择输出电流更大、上升下降时间更短的驱动芯片。

- 减小MOS管输入电容影响:可以采用一些特殊的驱动电路拓扑结构,如推挽式驱动等,来减小MOS管输入电容对驱动信号上升下降时间的影响。

- 关于在DS之间并联电容的分析:

- 并联电容抑制振荡的原理:- 当MOS管开通和关断时,寄生电感会产生尖峰电压,导致振荡。并联电容后,电容可以在MOS管开通时吸收能量,在关断时释放能量,从而抑制尖峰电压,达到抑制振荡的目的。例如,当MOS管关断瞬间,寄生电感产生的感应电动势会使DS间电压升高,此时电容会吸收这部分能量,避免电压过高产生振荡。

- 并联电容加剧驱动信号过缓及增大损耗的原因:

- 驱动信号上升时,电容需要充电,这会增加驱动电路的负载,导致驱动信号上升沿更缓。下降时电容放电,同样会影响信号下降沿。例如,假设驱动信号源内阻为R,电容为C,当驱动信号上升时,电容充电电流(I = \frac{V}{R})(V为驱动信号电压),电容充电时间常数(τ = RC),充电时间会随着C的增大而变长,从而使驱动信号上升沿变缓。

- 电容在充放电过程中会消耗能量,这就增大了电路的损耗。

- 总结:

- boost升压电路中MOS管驱动信号过缓及振荡是由多种因素导致的,包括寄生电感、驱动能力不足和MOS管输入电容等。

- 解决驱动信号问题需要从优化布线、增强驱动能力等方面入手。而在DS间并联电容虽能抑制振荡,但会带来驱动信号过缓及增大损耗的问题,在实际应用中需要综合考虑各种因素,权衡利弊来选择合适的解决方案。

例如,以一个简单的boost升压电路为例,假设原来的驱动电路输出能力有限,导致MOS管开通时间长,上升沿过缓。通过更换为输出能力更强(上升下降时间更短)的驱动芯片后,驱动信号上升沿和下降沿明显变快,电感电流波动也减小。如果之前在DS间并联电容抑制了振荡,但驱动信号变缓,此时可以尝试先优化布线,看是否能在不增加电容的情况下改善振荡问题,若不行,再考虑调整电容值或采用其他抑制振荡的方法,同时尽量减小对驱动信号的影响。

希望以上解答对您有所帮助。如果您有任何疑问,欢迎在评论区提出。

关注

关注