这个原文件是PADS9.5发过来的,打开后修改了下,发现覆铜上面做的禁止区域会把一些GND的引脚直接隔绝覆铜,哪位可以帮忙分析下

这个原文件是PADS9.5发过来的,打开后修改了下,发现覆铜上面做的禁止区域会把一些GND的引脚直接隔绝覆铜,哪位可以帮忙分析下

下午好🌅🌅🌅

本答案参考通义千问

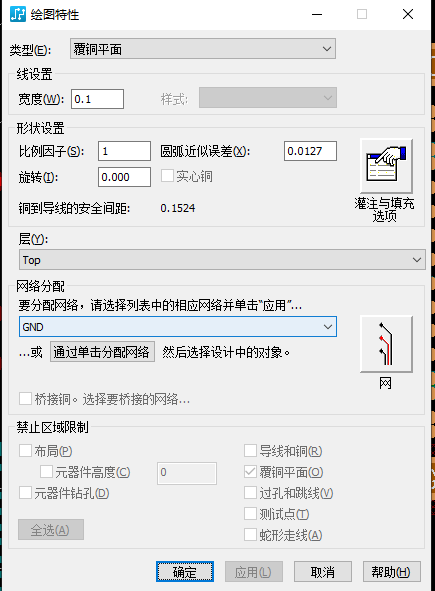

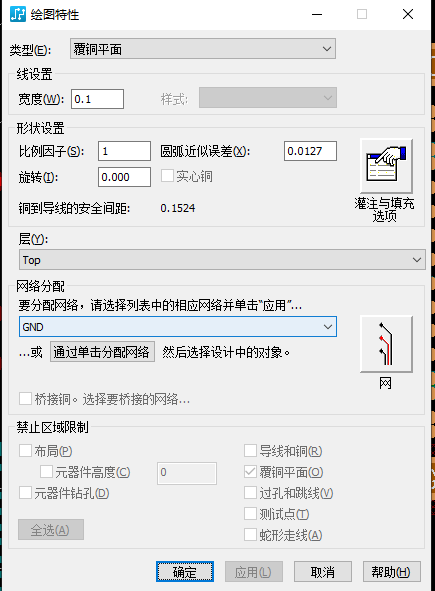

在使用 PADS VX(或旧版本如 PADS 9.5)进行 PCB 设计时,覆铜设置中的“禁止区域”(Keepout Area) 会阻止覆铜(Copper Pour)覆盖该区域。然而,有时会出现某些 GND 引脚被错误地隔绝在覆铜之外的情况,这可能是由以下几个原因导致的:

以下是详细的解决步骤:

Keepout 或 Board Outline 层)。重点:禁止区域应仅限制在板框或特定器件周围,不应覆盖任何 GND 引脚。

GND)。重点:所有 GND 引脚必须连接到同一个网络,并且该网络应与覆铜设置的网络一致。

GND。重点:覆铜的网络必须与 GND 引脚的网络一致,否则覆铜不会覆盖这些引脚。

GND。重点:每次修改后务必重新运行覆铜,确保所有引脚都能被正确连接。

重点:通过第三方工具验证可以更直观地发现覆铜问题。

如果你使用的是 PADS Scripting 或 Scripting API 来自动调整覆铜或禁止区域,可以参考以下伪代码结构:

# 示例:调整禁止区域

def adjust_keepout_area():

# 获取当前 PCB

pcb = get_current_pcb()

# 遍历所有元件

for component in pcb.get_components():

if component.is_gnd():

# 获取所有 GND 引脚

gnd_pins = component.get_gnd_pins()

# 调整禁止区域,确保不覆盖 GND 引脚

for pin in gnd_pins:

keepout_layer = pcb.get_layer("Keepout")

keepout_layer.remove_pin_from_keepout(pin)

# 更新覆铜

copper_pour = pcb.get_copper_pour("GND")

copper_pour.update()

# 调用函数

adjust_keepout_area()

注意: 上述代码仅为示例,实际需根据 PADS 的 API 编写。

| 问题 | 原因 | 解决方法 | |------|------|----------| | GND 引脚未被覆铜覆盖 | 禁止区域错误覆盖 | 调整或删除错误的禁止区域 | | GND 引脚未连接到覆铜网络 | 电气属性设置错误 | 检查并设置正确的 GND 网络 | | 覆铜规则限制 | 设置不合理 | 修改覆铜规则,确保连接方式正确 |

如你有具体的文件或截图,也可以提供,我可以进一步帮你定位问题所在。