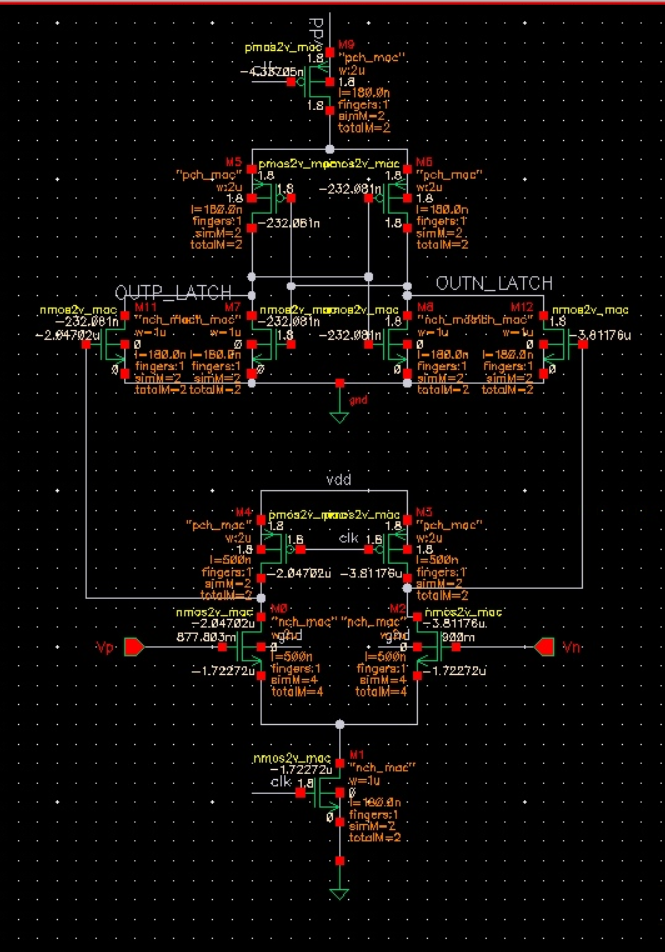

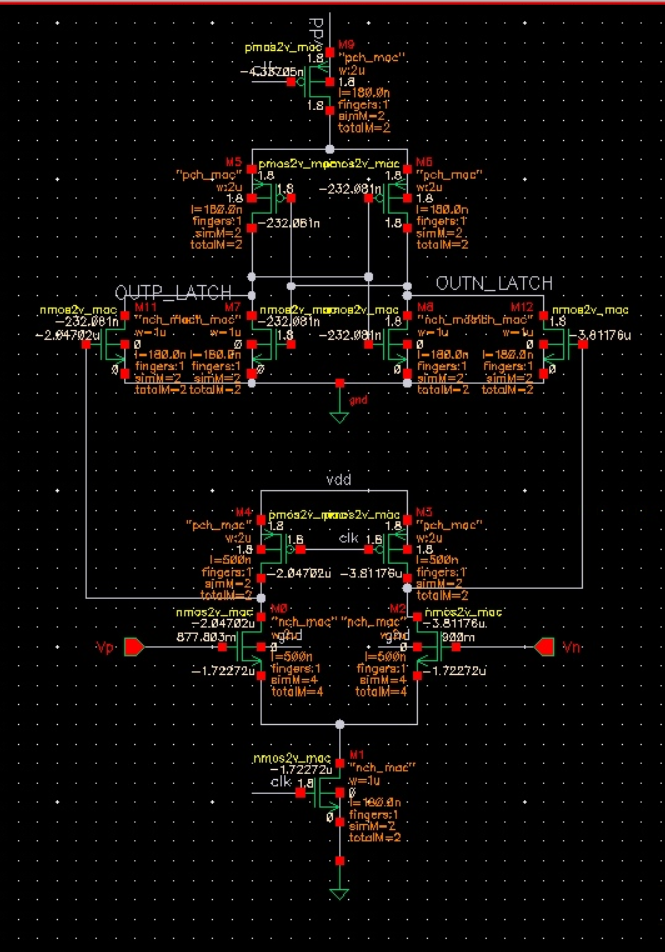

双尾比较器

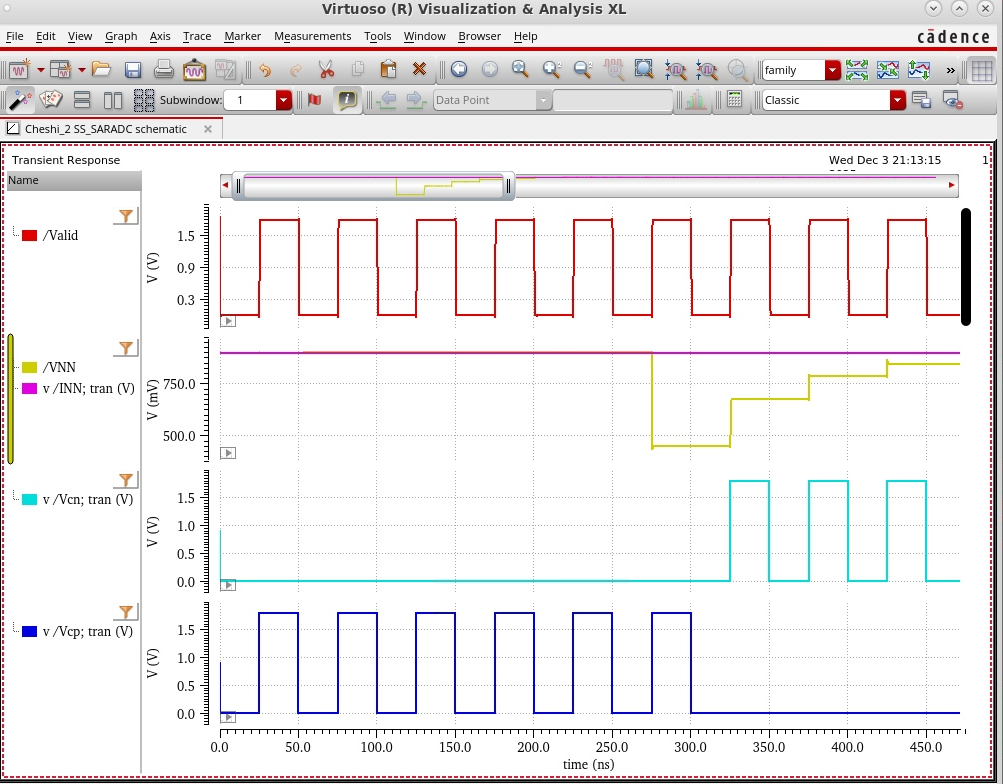

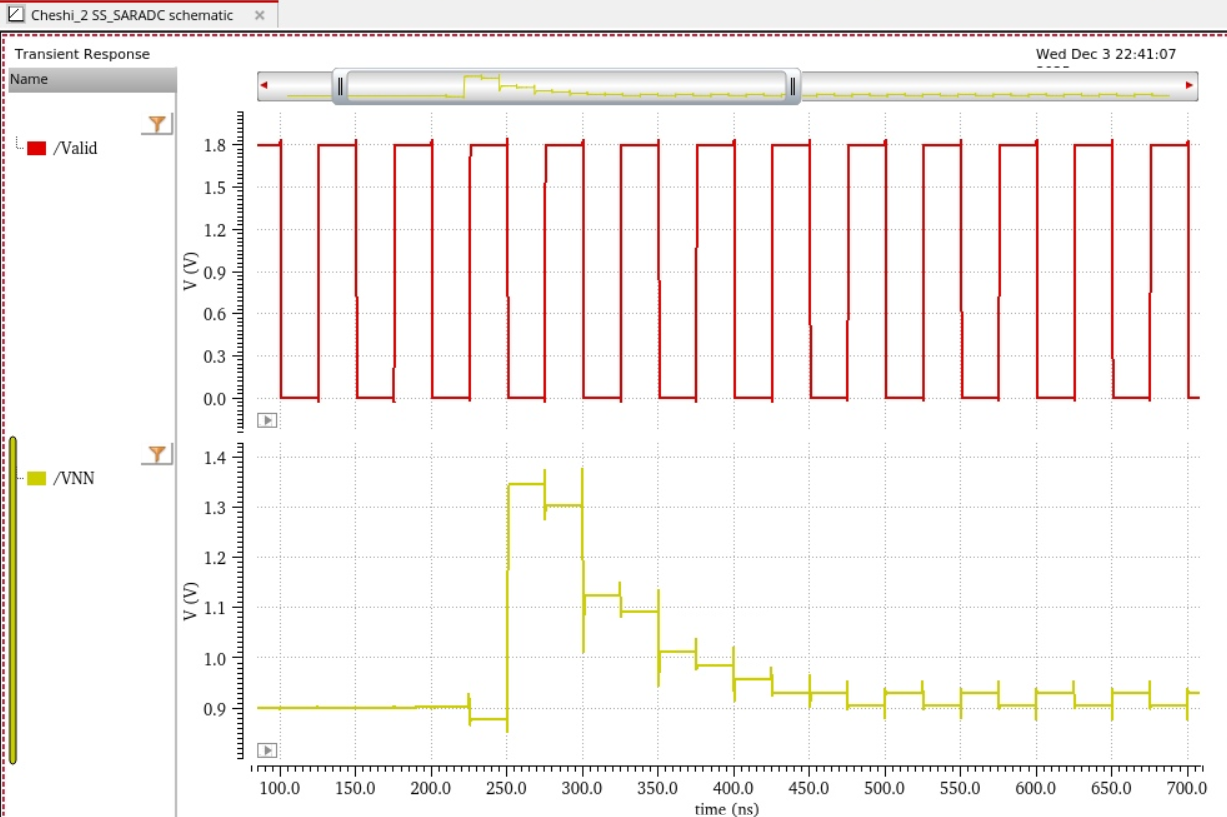

理想波形

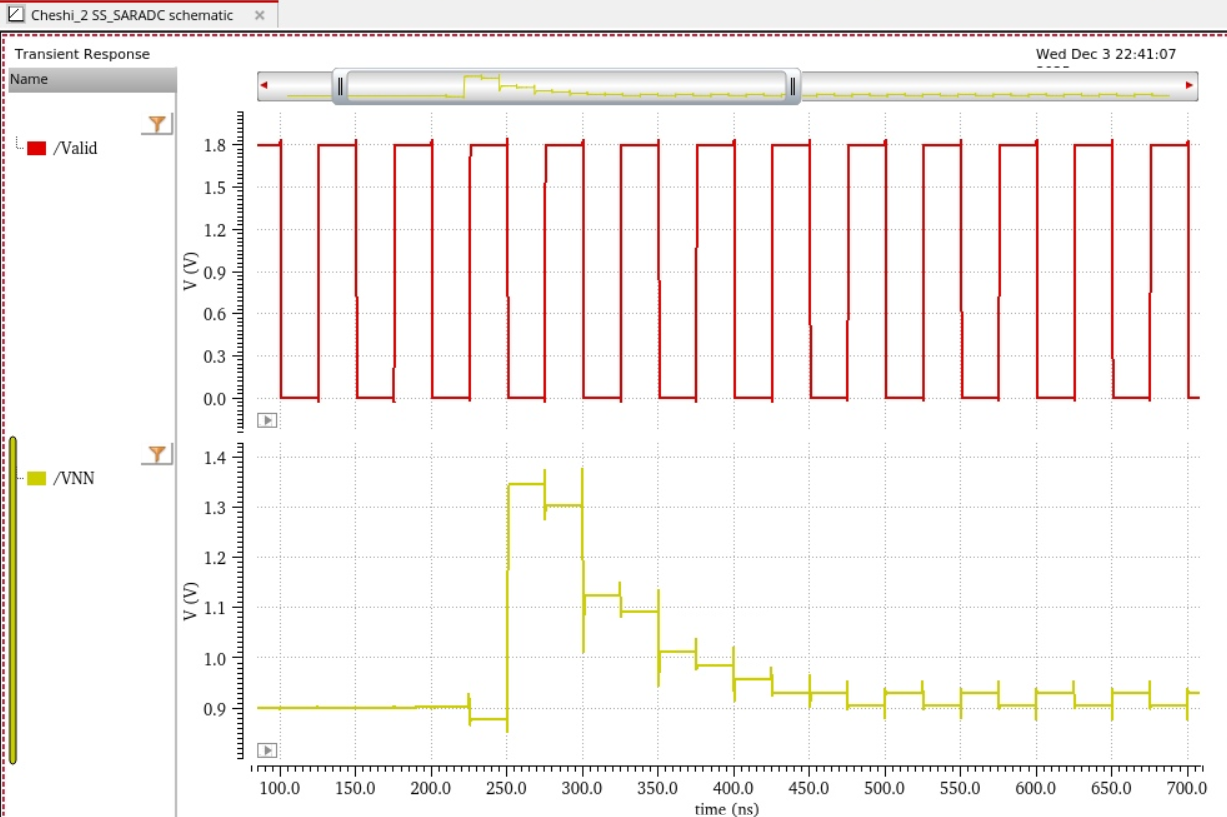

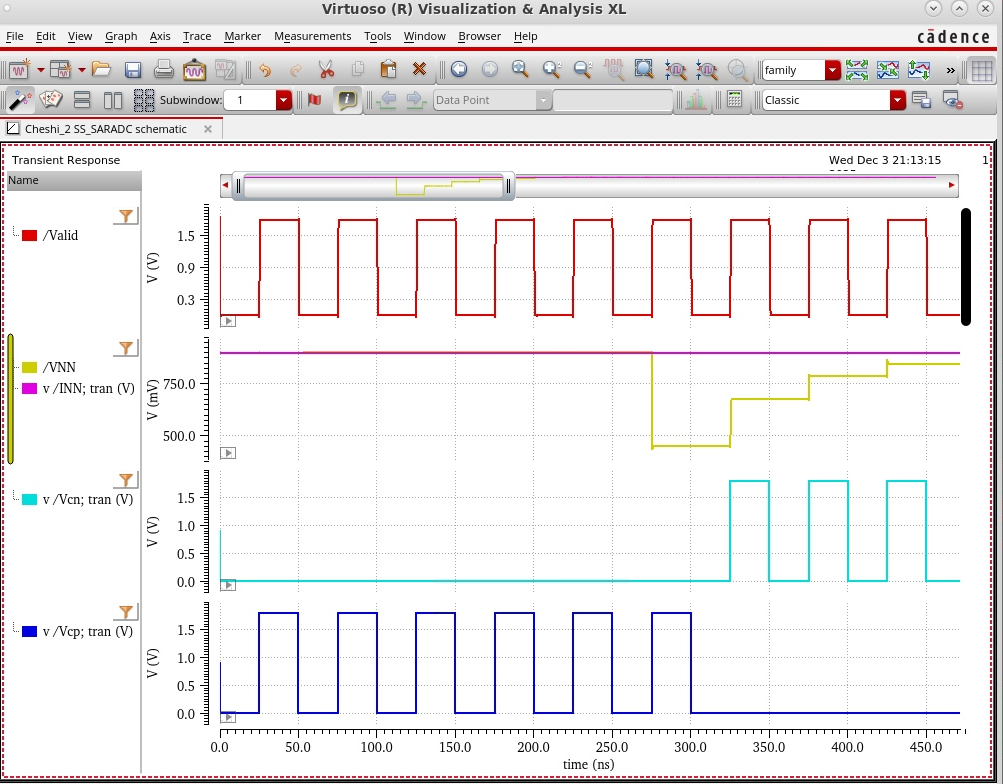

换上比较器后的波形

应该是动态比较器的原因,因为是发生在clk信号跳变的时候。但是不知道怎么修改

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

问题分析

根据你的描述,问题是关于SAR ADC(Successive Approximation Register Analog-to-Digital Converter)硬件设计的。具体来说,你将VerilogA比较器换成了自己搭的比较器后,CDAC(Charge-Discharge Amplifier)输出跳变。

可能原因

解决方案

核心代码

module comparator(

input logic clk,

input logic reset,

input logic [7:0] in1,

input logic [7:0] in2,

output logic out

);

always @(posedge clk) begin

if (reset) begin

out <= 0;

end else begin

if (in1 > in2) begin

out <= 1;

end else begin

out <= 0;

end

end

end

endmodule

注意

上述代码仅供参考,具体的设计和实现需要根据实际情况进行调整和优化。