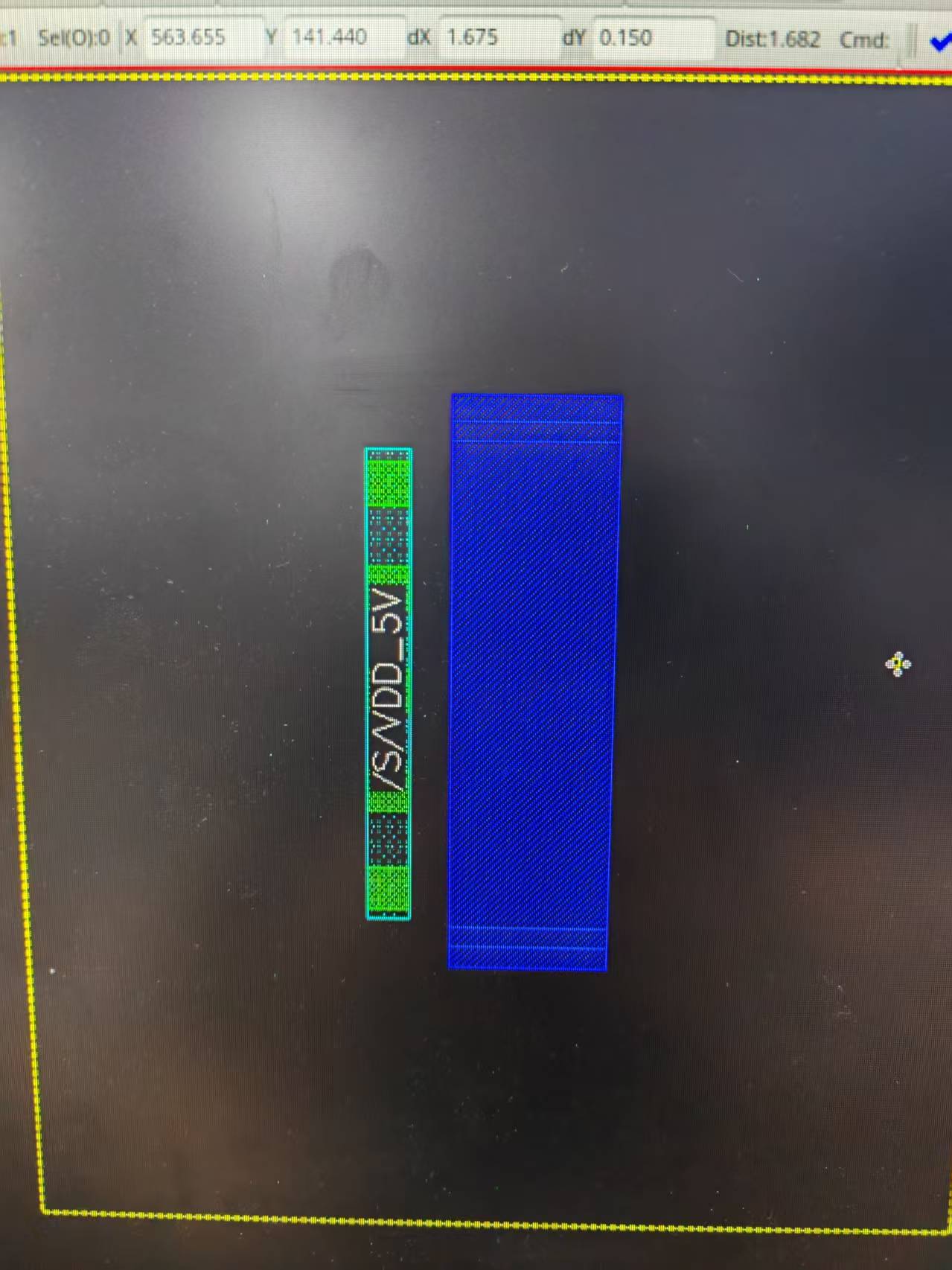

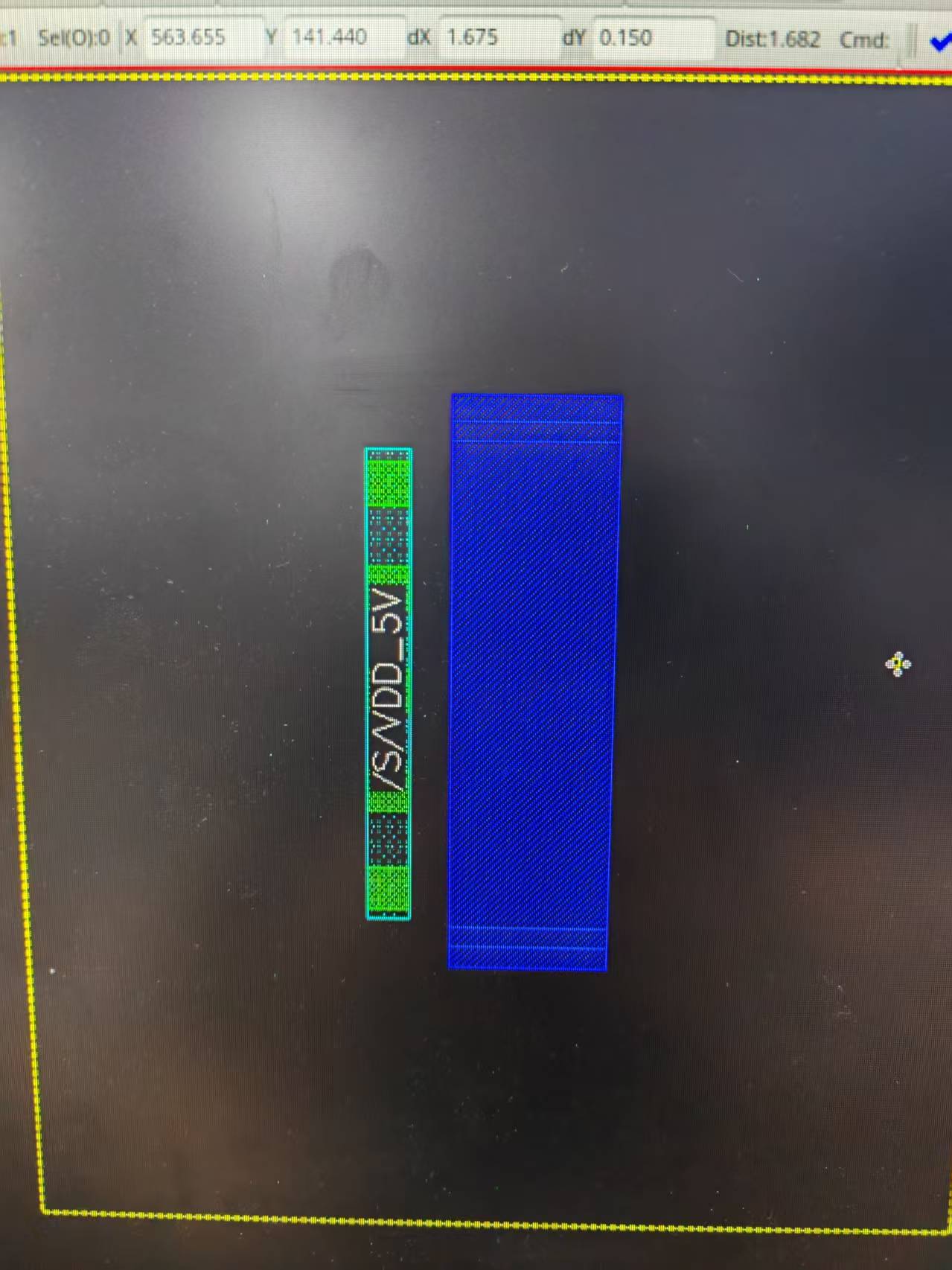

如下图,在IC618画版图的时候,调用出来的器件,S/D端总是只有一半显示,这是什么原因啊?

如下图,在IC618画版图的时候,调用出来的器件,S/D端总是只有一半显示,这是什么原因啊?

晚上好🌙🌙🌙

本答案参考通义千问

在使用 IC618(通常指 Cadence 的 Virtuoso IC 6.1.8)进行版图设计时,如果调用出来的器件(如 MOSFET、二极管等)的 S/D 端(源/漏端)只显示一半,可能是由以下原因导致的:

.lib 文件或 .lef 文件是否包含完整的 S/D 端图形。重点提示:确保你使用的器件库是经过验证的,且与当前工艺节点匹配。

SD, DRAIN, SOURCE 等)是否被激活并可见。重点提示:某些层可能因权限或配置问题未被显示,需手动启用。

重点提示:若器件为自定义模型,建议检查其 SPICE 参数与版图定义是否一致。

.tech 或 .lyt 文件),检查 S/D 端相关的层定义。重点提示:技术文件的配置直接影响版图的显示效果,务必仔细检查。

重点提示:保持软件版本更新是避免此类问题的有效手段。

如果你是在脚本中调用器件(如通过 sketch 脚本),可以检查如下代码是否存在问题:

create_cell -type layout -view layout -library my_lib -cell my_cell

修改建议:

# 确保器件的版图视图正确加载

set cell [get_db cells -filter "name == my_cell"]

set view [get_db views -filter "cell == $cell and name == layout"]

set layer [get_db layers -filter "name == SD"] # 检查 S/D 层是否存在

if { $layer != "" } {

set_layer_visible $layer true

}

重点提示:以上代码仅为示例,具体实现需根据你的项目结构和库文件进行调整。

| 原因 | 解决方案 |

|------|----------|

| 器件库配置错误 | 检查 .lib 或 .lef 文件,确保 S/D 端定义完整 |

| 版图视图设置问题 | 检查 Layer 设置,确保 S/D 层可见 |

| 器件参数错误 | 检查 W/L 等参数,必要时手动调整 |

| 工艺文件配置问题 | 检查 .tech 文件中 S/D 层定义 |

| 软件版本兼容性 | 升级或修复 Virtuoso 软件 |

如有需要,也可以提供具体截图或器件名称,我可以进一步帮助你定位问题。