晚上好🌙🌙🌙

本答案参考通义千问

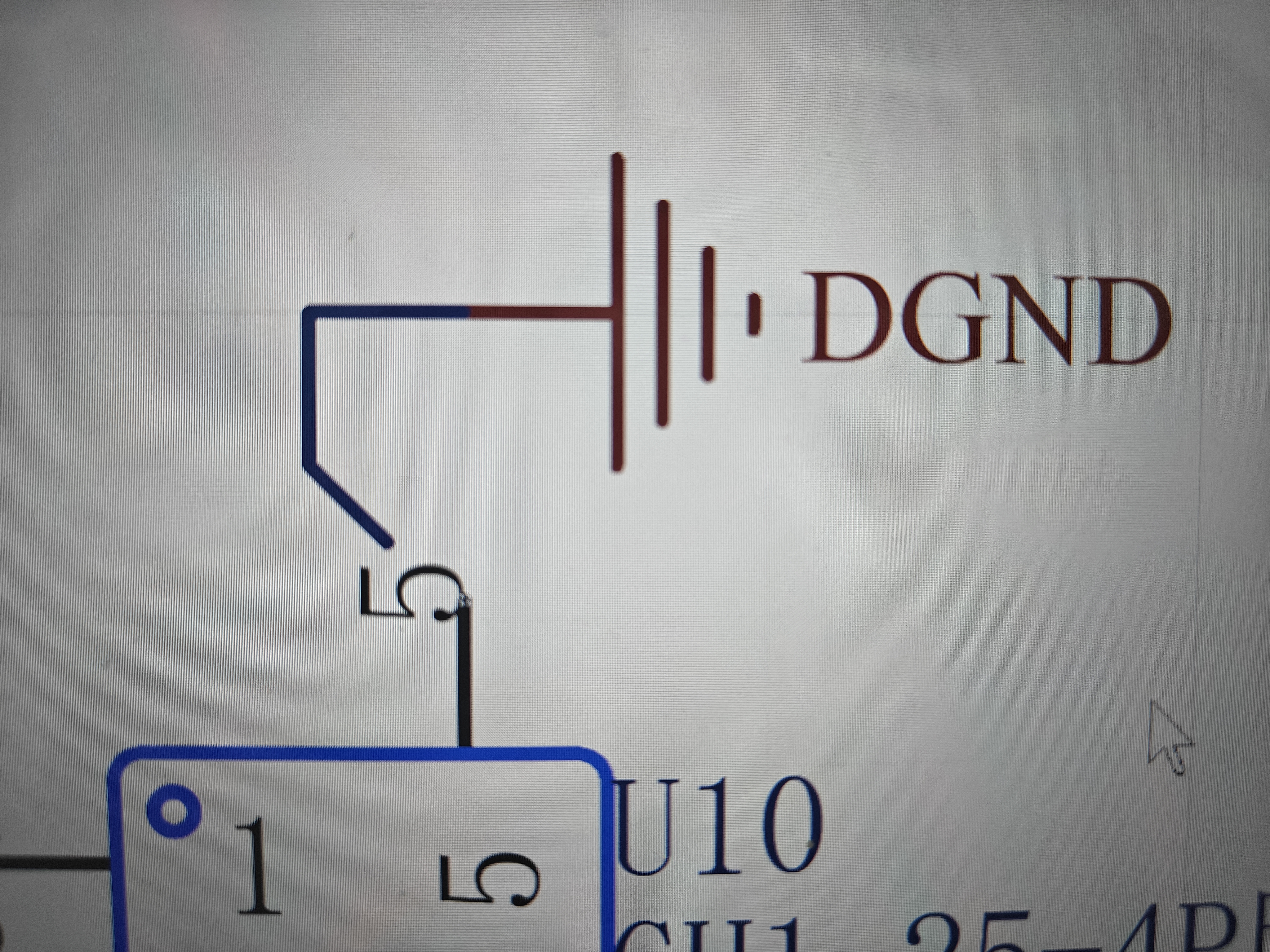

在使用Altium Designer(AD)进行原理图绘制时,如果遇到芯片的第5脚(如VDD、GND等)无法与DGND相连的问题,通常是由于以下几种原因导致的。以下是详细的分析和解决方案:

一、问题分析

-

引脚名称不匹配

- 芯片的第5脚可能被定义为“VDD”或“AVDD”,而你试图连接的是“DGND”。

- 原理图中需要确保两个网络名称一致。

-

未正确设置网络标签(Net Label)

- 如果没有使用正确的网络标签(如“DGND”),则无法实现电气连接。

-

未使用“Power Port”或“Ground Symbol”

- 对于电源和地信号,建议使用标准的电源符号(如“+5V”、“GND”)来确保电气连通性。

-

图纸中存在多个“DGND”网络

- 可能存在多个同名但未连接的“DGND”网络,导致系统无法识别。

-

未启用电气规则检查(ERC)

二、解决方案

1. 检查并确认引脚名称

- 打开芯片的封装库(Library)或原理图符号(Symbol)。

- 检查第5脚是否被命名为“DGND”或“GND”。

- 如果不是,修改为“DGND”。

重点:确保芯片引脚名称与你要连接的网络名称一致。

2. 使用正确的网络标签(Net Label)

- 在原理图中添加一个“Net Label”。

- 输入“DGND”作为网络名称。

- 将该网络标签与芯片的第5脚连接。

重点:网络标签是实现电气连接的关键工具。

3. 使用标准电源符号(Power Port)

- 如果芯片第5脚是电源(如VDD)或地(如DGND),推荐使用标准的电源符号。

- 在AD中,可以使用“Power Port”工具,选择“DGND”或“GND”。

重点:使用标准电源符号可以提高可读性和电气连通性。

4. 检查是否有多个“DGND”网络

- 在原理图中,右键点击“Project” -> “Options” -> “Net Classes”。

- 确保“DGND”网络只出现一次。

- 如果有重复,删除多余的网络。

5. 运行电气规则检查(ERC)

- 在AD中,点击“Tools” -> “Electrical Rules Check (ERC)”。

- 运行后查看是否有错误提示,特别是关于“Unconnected Net”或“Multiple Net Labels”。

重点:ERC可以帮助发现潜在的电气连接问题。

三、示例代码(原理图连接)

假设你有一个芯片 U1,其第5脚应连接到 DGND,操作步骤如下:

- 在原理图中放置一个“Net Label”。

- 输入网络名称:“DGND”。

- 使用导线(Wire)将 DGND 网络标签连接到 U1 的第5脚。

- 保存并运行 ERC。

[原理图示例]

U1 (芯片)

|

+-- Pin 5 --> [Net Label: DGND]

四、常见错误排查

| 错误现象 | 解决方法 |

|----------|----------|

| 引脚无法连接 | 检查引脚名称是否与网络名称一致 |

| 无法识别 DGND | 添加正确的网络标签或电源符号 |

| 多个 DGND 网络 | 删除重复的网络标签 |

| 未报错但无法连接 | 运行 ERC 检查电气规则 |

五、总结

- 确保引脚名称与网络名称一致。

- 使用网络标签或电源符号进行连接。

- 运行 ERC 检查电气连通性。

- 避免重复网络标签。

如果你能提供具体的芯片型号或原理图截图,我可以进一步帮助你定位具体问题。