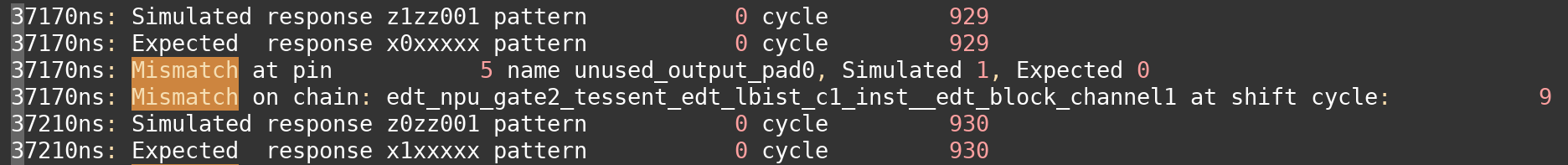

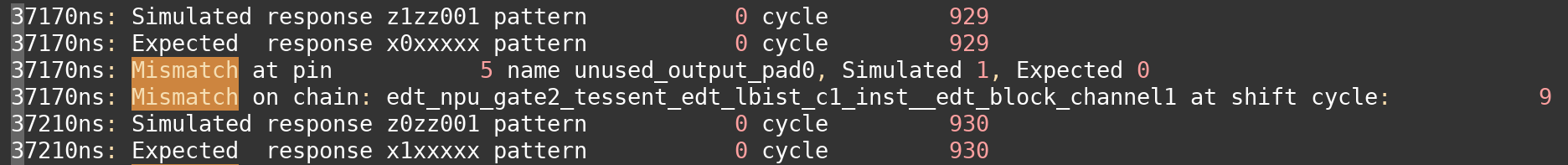

在用VCS对pattern执行chain serial或scan serial的仿真时,出现Mismatch如下,但这是serial的仿真,且有EDT压缩逻辑,这里无法报出具体的reg,我该怎么定位到是哪条chain的哪个reg出现的Mismatch呢?

在用VCS对pattern执行chain serial或scan serial的仿真时,出现Mismatch如下,但这是serial的仿真,且有EDT压缩逻辑,这里无法报出具体的reg,我该怎么定位到是哪条chain的哪个reg出现的Mismatch呢?

下午好🌅🌅🌅

本答案参考通义千问

在使用 VCS 进行 Serial Scan 或 Chain Serial 仿真 时,如果出现 Mismatch,但因为有 EDT(Embedded Deterministic Test)压缩逻辑 的存在,导致无法直接定位到具体的 Register(reg),这是比较常见的问题。以下是一个详细的解决方案和定位方法:

为了定位到是哪条 chain 的哪个 reg 出现了 mismatch,可以按照以下步骤进行:

VCS 提供了一些调试选项,可以帮助你查看压缩后的 scan chain 数据和对应的原始寄存器地址。

+vcs+dump+ 参数vcs -R +vcs+dump+all -timescale=1ns/1ps +access+all +define+TESTMODE=1 +define+EDT_ENABLE=1

+vcs+dump+all:启用所有信号的 dump,包括压缩后的 scan chain 和原始寄存器。+access+all:确保所有寄存器都能被访问。+define+EDT_ENABLE=1:确保 EDT 逻辑被正确启用。+vcs+trace+ 参数vcs -R +vcs+trace+all -timescale=1ns/1ps +access+all +define+TESTMODE=1 +define+EDT_ENABLE=1

+vcs+trace+all:记录所有信号的波形,便于后续分析。wave 工具查看压缩后的 scan chainwave 工具,查看压缩后的 scan chain 数据。wave -i <trace_file.fsdb>

如果你能访问到 RTL 设计文件,可以尝试以下方法来辅助定位:

你可以修改仿真脚本,添加一些调试信息,例如:

# 在仿真脚本中添加如下命令

set sim_options "-R +vcs+dump+all +access+all +define+TESTMODE=1 +define+EDT_ENABLE=1"

或者在仿真过程中,动态打印某些 scan chain 的内容:

# 在仿真过程中执行以下命令

simulator->print("Scan_chain_0_data", "Scan_chain_0_data");

simulator->print("Scan_chain_1_data", "Scan_chain_1_data");

| 工具/方法 | 用途 | |----------|------| | VCS Waveform Viewer | 查看压缩后的 scan chain 数据 | | EDT 解码工具 | 将压缩数据还原为原始寄存器值 | | Design Compiler / DC Shell | 分析 scan chain 结构 | | Verdi | 高级波形分析工具,支持 EDT 解码 |

要定位 EDT 压缩下的 serial scan 仿真 mismatch,你需要:

+vcs+dump+all);# 修改后的仿真脚本示例

vcs -R +vcs+dump+all +access+all +define+TESTMODE=1 +define+EDT_ENABLE=1 \

+vcs+trace+all \

-timescale=1ns/1ps \

-sverilog \

-f design_files.f \

-o simv

如果你能提供具体的 Mismatch 报告内容 或 scan chain 的结构描述,我可以进一步帮你定位到具体的 register!