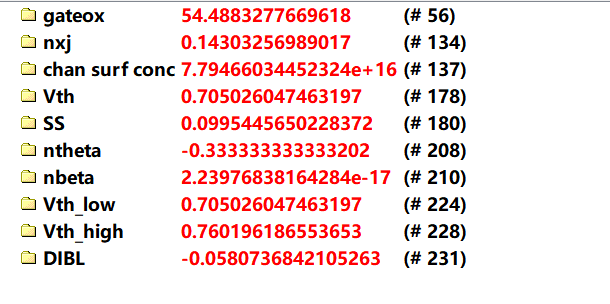

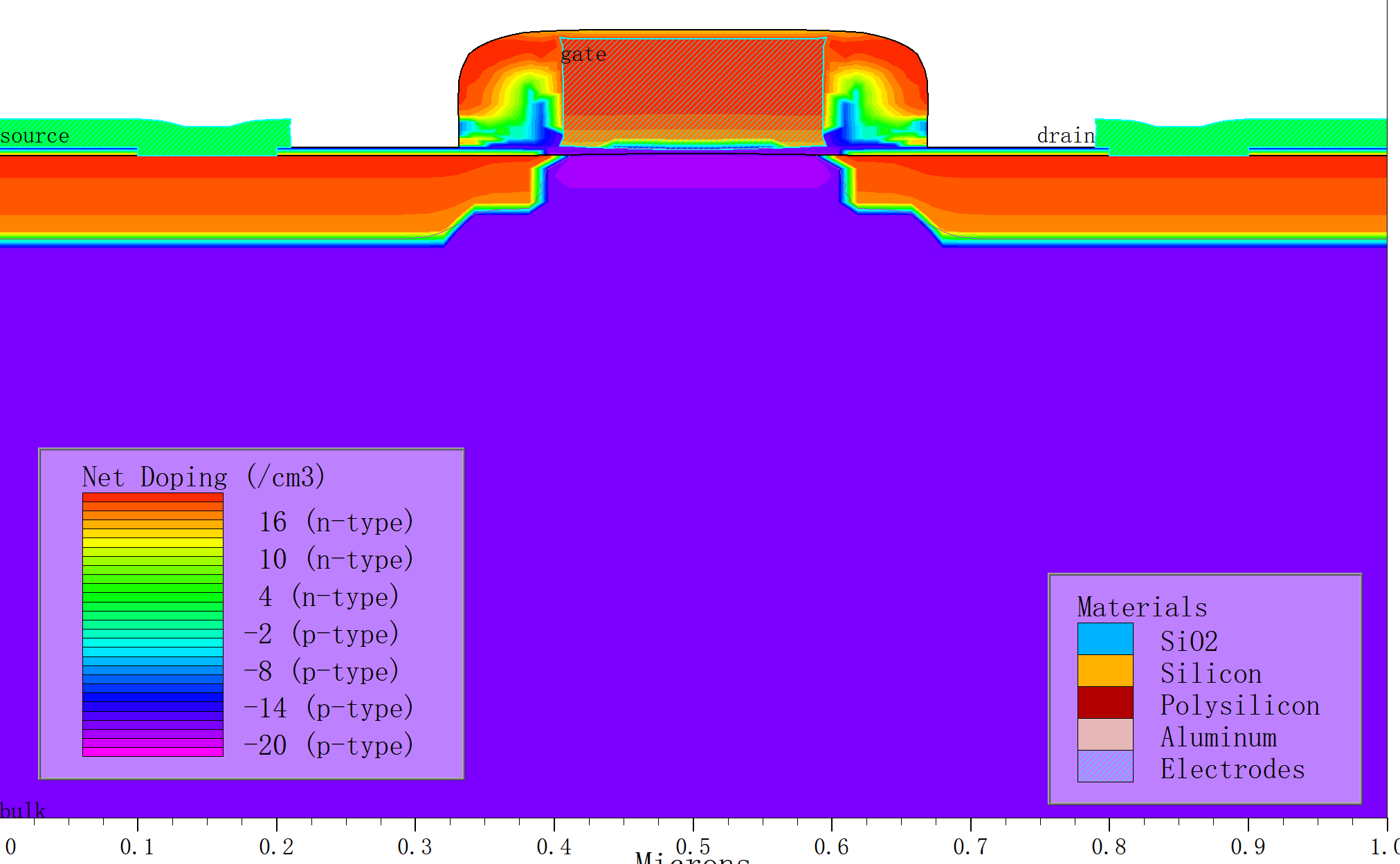

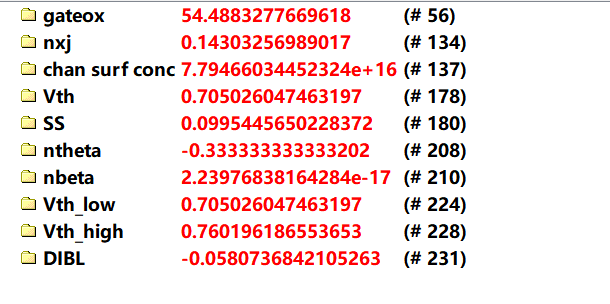

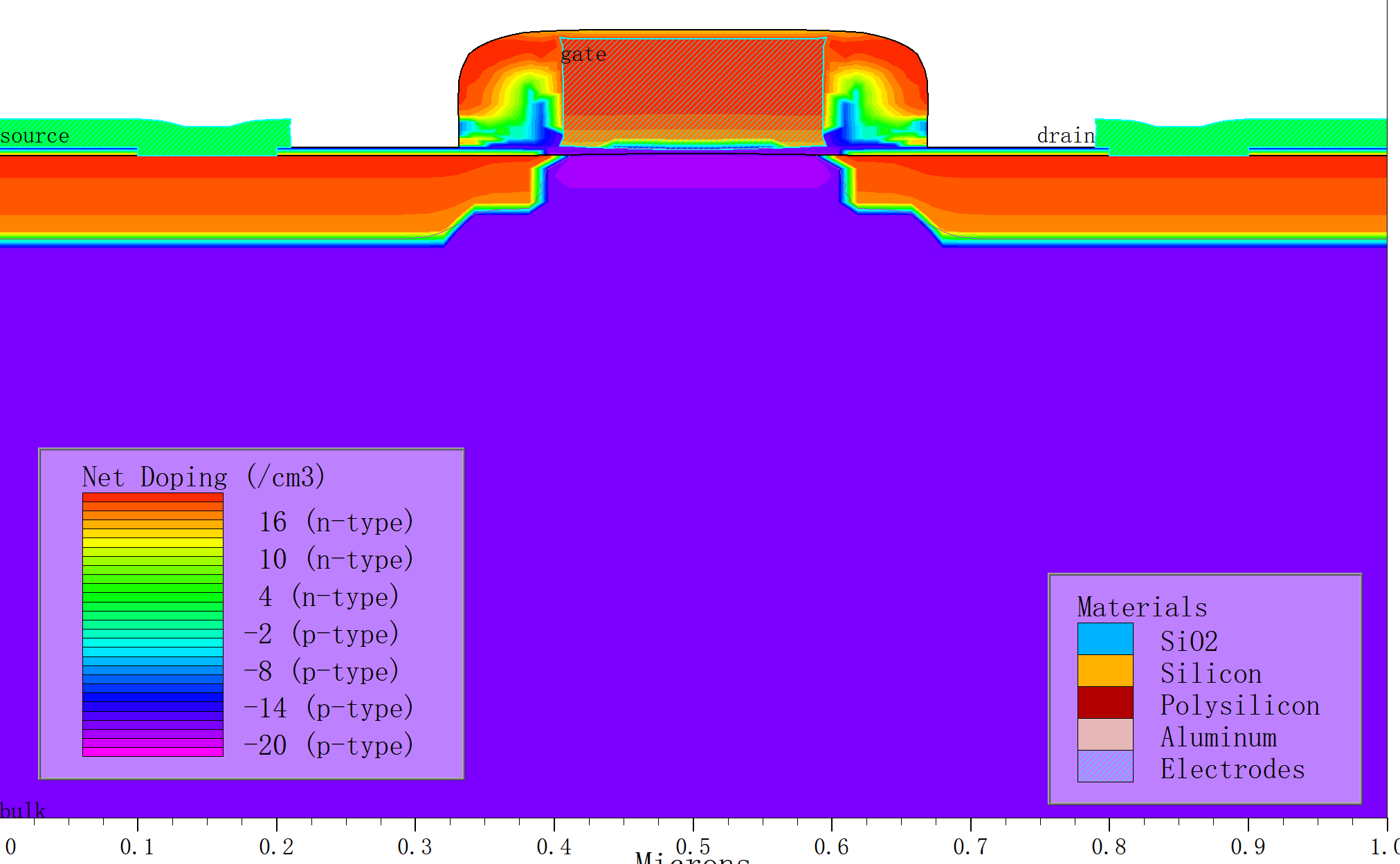

可以看到,使用idvg曲线求阈值电压,在加大vds后,本应该阈值电压下降,现在却上升,大家遇到过这种问题吗,如何解决。

可以看到,使用idvg曲线求阈值电压,在加大vds后,本应该阈值电压下降,现在却上升,大家遇到过这种问题吗,如何解决。

晚上好🌙🌙🌙

本答案参考通义千问

在180nm NMOS器件仿真中,DIBL(Drain Induced Barrier Lowering,漏致势垒降低)指标为负是一个不正常的现象,通常意味着仿真设置、模型参数或物理机制存在异常。以下是详细分析和解决方案:

DIBL 是衡量 MOSFET 在高漏极电压下,阈值电压随漏极电压变化的敏感程度。其定义如下:

$$ \text{DIBL} = \frac{\Delta V_{th}}{\Delta V_{DS}} $$

根据你的描述,“在加大 $V_{DS}$ 后,本应该阈值电压下降,现在却上升”,这说明仿真中出现了以下可能问题:

L(沟道长度)W(宽度)TOX(氧化层厚度)NSUB(衬底掺杂浓度)VTH0(初始阈值电压)确认仿真方法是否正确

检查模型参数

调整仿真条件

修正 DIBL 计算逻辑

使用工具辅助验证

import numpy as np

# 假设我们有以下数据

Vds_values = [0.5, 1.0, 1.5] # 不同的 Vds 值

Vth_values = [0.6, 0.55, 0.6] # 对应的 Vth 值(假设这里出现反常)

# 计算 DIBL

def calculate_DIBL(Vds_list, Vth_list):

if len(Vds_list) != len(Vth_list):

raise ValueError("Vds and Vth lists must have the same length.")

dVth = Vth_list[-1] - Vth_list[0]

dVds = Vds_list[-1] - Vds_list[0]

DIBL = dVth / dVds

return DIBL

DIBL_result = calculate_DIBL(Vds_values, Vth_values)

print(f"Calculated DIBL: {DIBL_result:.3f} V/V")

⚠️ 注意:上述示例中,若 $V_{th}$ 随 $V_{DS}$ 增加而增大,则 DIBL 为正,这可能是不正常的。

| 问题 | 原因 | 解决方案 | |------|------|----------| | DIBL 为负 | 仿真方法错误 | 使用饱和区提取 $V_{th}$ | | DIBL 为负 | 模型参数错误 | 校准模型参数,确保工艺匹配 | | DIBL 为负 | 数据处理错误 | 检查 DIBL 公式和 $V_{DS}$ 变化方向 | | DIBL 为负 | 仿真条件异常 | 控制 $V_{DS}$ 范围,避免击穿 |

如果你能提供具体的仿真数据或代码片段,我可以进一步帮助你定位问题!