使用74LS160和74LS48,显示器数字显示太快,时钟调10Hz,显示出错

上午好☀️☀️☀️️

本答案参考通义千问

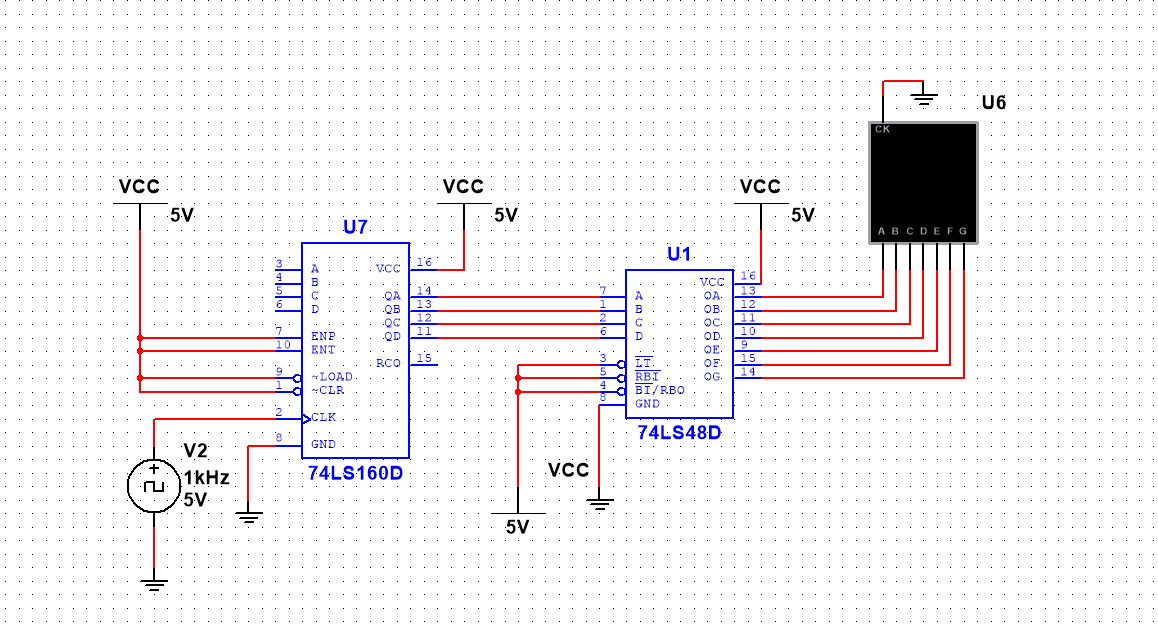

在使用 Multisim 进行电路仿真时,如果你使用 74LS160(十进制计数器) 和 74LS48(七段数码管译码器) 来实现数字显示,并且发现“显示器数字显示太快,时钟调到10Hz,显示出错”,这通常是由以下几个原因导致的:

确保时钟源设置为 10Hz:

添加时钟分频器(可选):

使用锁存器(如 74LS373):

LE 引脚)来锁存当前状态。74LS160 输出 → 74LS373 输入

74LS373 输出 → 74LS48 输入

示例电路连接方式:

Clock (10Hz) → 74LS160 CLK

74LS160 Q0-Q3 → 74LS373 D0-D3

74LS373 LE → 逻辑高电平(常开)

74LS373 Q0-Q3 → 74LS48 A-D

74LS48 输出 → 数码管

使用 Multisim 的探针(Probe) 或 波形查看器(Oscilloscope) 观察以下信号:

确认信号是否稳定,是否有毛刺或抖动。

[Clock 10Hz]

↓

[74LS160] (Counter)

↓

[74LS373] (Latch)

↓

[74LS48] (Decoder)

↓

[Seven-Segment Display]

74LS160:

74LS373:

74LS48:

重点问题:

时钟频率设置不当或未稳定显示信号 导致数码管显示异常。

解决重点:

1. 确保时钟为 10Hz 并稳定;

2. 使用 74LS373 锁存器稳定显示;

3. 正确连接 74LS48 与数码管。

如有需要,我可以为你提供 Multisim 电路图的截图或文件模板,欢迎继续提问!