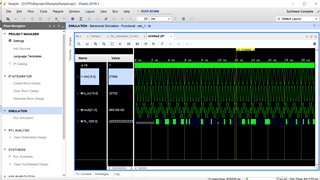

做了一个简易的数字下变频模块,用DDS分别生成2Mhz与3Mhz的正弦波输出分别设为16位宽的

din,s_oc,两波混频,然后通过低通滤波器滤除混频产生的5Mhz正弦波,但是滤出波形全输出不对?

这是我的代码。

module hunp(

input clk,

output signed [15:0] din ,

output signed [15:0] s_oc ,

output signed [31:0] mult ,

output signed [55:0] fir_1

);

wire m_axis_phase_tdata1;

wire m_axis_phase_tdata2;

wire fir_1;

dds_compiler_0 dds1 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(din), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata1) // output wire [31 : 0] m_axis_phase_tdata

);

dds_compiler_1 dds2 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(s_oc), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata2) // output wire [31 : 0] m_axis_phase_tdata

);

mult_gen_0 mult0 (

.CLK(clk), // input wire CLK

.A(din), // input wire [15 : 0] A

.B(s_oc), // input wire [15 : 0] B

.P(mult) // output wire [31 : 0] P

);

fir_compiler_0 your_instance_name (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(1), // input wire s_axis_data_tvalid

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata(mult), // input wire [31 : 0] s_axis_data_tdata

.m_axis_data_tvalid( ), // output wire m_axis_data_tvalid

.m_axis_data_tdata(fir_1) // output wire [55 : 0] m_axis_data_tdata

);

endmodule

验证代码如下:

module tb();

reg clk;

wire signed [15:0] din;

wire signed [15:0] s_oc;

wire signed [31:0] mult;

wire signed [55:0] fir_1;

hunp hunp1(

.clk(clk),

.din (din ),

.s_oc (s_oc ),

.mult (mult ),

.fir_1 (fir_1)

);

initial

begin

clk = 0;

end

//产生10MHz时钟信号

always

begin

#10 clk = ~clk;

end

endmodule

望博学多才的各位批评指正。