module dds ( clk , reset , div , choose , data );

input [5:0] div ;

input [1:0] choose ;

input clk , reset ;

output [7:0] data ;

wire [7:0] data ;

reg [5:0] addr , address ;

reg [5:0] i ;

reg clkdiv ;

function [7:0] rom ;

input [5:0] address ;

begin

case ( address )

0:rom=0;

1: rom =4;

2: rom =12;

3: rom =21;

4:rom=25;

5:rom=21;

6:rom=12;

7:rom=4;

8: rom =20;

9:rom=20;

10:rom=20;

11:rom=20;

12:rom=1;

13: rom =1;

14:rom=1;

15:rom=1;

16:rom=0;

17: rom =5;

18:rom=10;

19:rom=15;

20: rom =20;

21: rom =25;

22: rom =30;

23: rom =35;

24:rom=35;

25: rom =30;

26:rom=25;

27: rom =20;

28:rom=15;

29:rom=10;

30:rom=5;

31: rom =0;

default:rom=10'hxx ;

endcase

end

endfunction

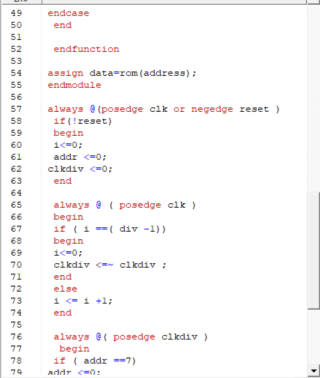

assign data=rom(address);

endmodule

always @(posedge clk or negedge reset )

if(!reset)

begin

i<=0;

addr <=0;

clkdiv <=0;

end

always @ ( posedge clk )

begin

if ( i ==( div -1))

begin

i<=0;

clkdiv <=~ clkdiv ;

end

else

i <= i +1;

end

always @( posedge clkdiv )

begin

if ( addr ==7)

addr <=0;

else

addr <= addr +1;

end

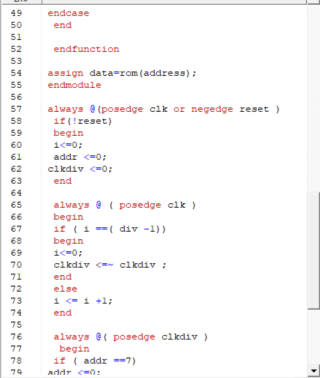

always @( posedge clkdiv )

begin

case ( choose )

0:address<= addr ;

1:address<= addr +8;

2:address<= addr +16;

3:address<= addr +24;

endcase

end

错误如下

** Error: D:/zhuomian/yuan.v(59): near "always": syntax error, unexpected always, expecting class