写了一个累加器

module DDS_Accumulator(

input wire clk_A_10kHz,

input wire rst_n,

input wire [7:0] switch,

output reg [7:0] sum

);

always@(posedge clk_A_10kHz or negedge rst_n)

begin

if(!rst_n)

sum <= 8'b00000000;

else

sum <= sum+ 8'b00000001;

end

endmodule

仿真代码如下

module DDS_Accumulator_sim;

reg clk_A_10kHz;

reg rst_n;

initial

begin

clk_A_10kHz = 0;

rst_n=0;

#100

rst_n=1;

end;

always #5000 clk_A_10kHz = ~clk_A_10kHz;

DDS_Accumulator u0 (

.clk_A_10kHz(clk_A_10kHz),

.rst_n(rst_n),

.switch(switch),

.sum(sum)

);

endmodule

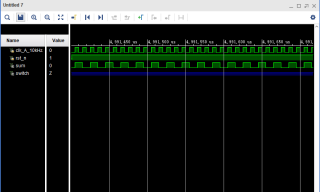

当我需要10kHz的clk时

always #5000 clk_A_10kHz = ~clk_A_10kHz;

延时设置为5000ns

此时的sum为啥是一位的internal signal?

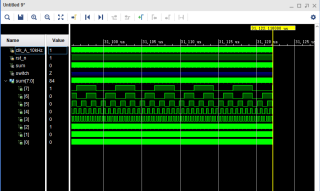

当我降低延时为10ns 提高clk频率时

能正常输出8位的sum

这是为什么呢