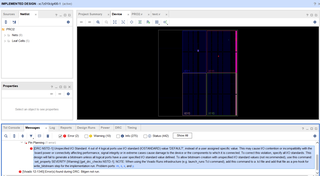

[DRC NSTD-1] Unspecified I/O Standard: 4 out of 4 logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting perfo

[Vivado 12-1345] Error(s) found during DRC. Bitgen not run.