FPGA如何对引脚进行分块?是由VCC的电压不同进行自行设计分块?还是每个块的引脚都是固定的?

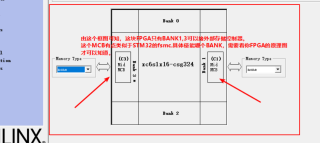

在进行DDR3与FPGA的硬件连接时,由FPGA的芯片手册得采用SSTL_15电压标准,即VDDQ=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片连接,是自己选择接口进行分块。再将该块上的VDDQ设置为1.5V,进行SSTL_15设置?还是只能连接在BANK1,3上且FPGA的分块是固定的。