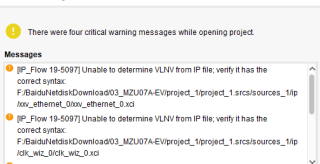

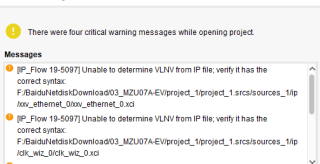

VIVADO出现错误[IP_Flow 19-5097] Unable to determine VLNV from IP file; verify it has the correct syntax,

VIVADO出现错误[IP_Flow 19-5097] Unable to determine VLNV from IP file; verify it has the correct syntax,

我之前也遇到过这个问题,通过这个解决了,你可以借鉴一下。

https://support.xilinx.com/s/question/0D52E00006hpp7v/dputrd%E7%BC%96%E8%AF%91%E5%A4%B1%E8%B4%A5?language=en_US