问题遇到的现象和发生背景

想要实现以下功能:

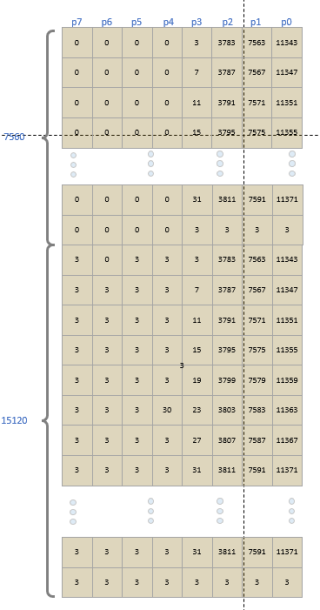

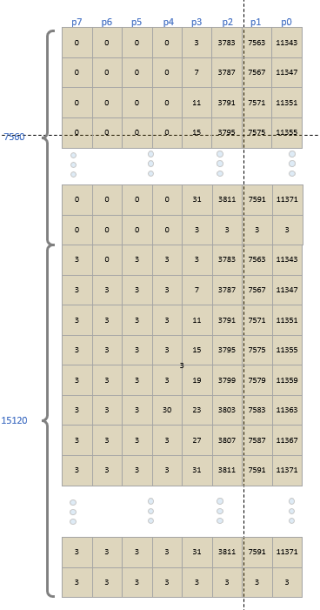

一个RAM宽度为8,深度为22680。其中前7560存放宽度为4,深度为7560的数据。让RAM的高4位或者低4位为0。剩下15120存放宽度为8,深度为15120的数据。这两个数据来自不同的模块。简单画图描述为如下:

目前想在已有的代码基础上更改,已有代码是存放4个宽度,深度为7560的RAM。

问题相关代码,请勿粘贴截图

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/06/15 08:53:20

// Design Name:

// Module Name: inputbuffer

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module SPAD_buffer(

input clk, //时钟

input asy_rst_n, //内码译码器复位信号,低电平有效

input i_en, //内码译码器使能信号,高电平有效

input i_rdy_SPAD, //SPAD输出标志

input i_SPAD_out, //SPAD输出的0/1数字信号

input [12:0] i_r_addr, //RAM1 PORTB读地址

output [3:0] o_r_data, //RAM1 PORTB读数据

output o_rdy1 //RAM1 PORTB ready

);

//-----------------------------------------------------------

wire [3:0] w_data; //RAM PORTA写数据

reg p0,p1,p2,p3;

reg wea; //RAM PORTA写使能

wire ena;

wire enb;

reg o_rdy1_reg;

reg [2:0] cnt_4;

reg [12:0] cnt_7560;

//assign w_data=wea?w_data_reg:4'dz;

assign w_data=(cnt_4==3'd4)?{p3,p2,p1,p0}:4'dz;

assign ena=wea||i_rdy_SPAD;

assign enb=o_rdy1;

always @(posedge clk )

begin

if(asy_rst_n)

begin

wea<=1'b0;

end

else wea<=i_rdy_SPAD;

end

always @(posedge clk )

begin

if(asy_rst_n)

begin

cnt_4<=3'd0;

cnt_7560<=13'd0;

p3<=1'b0;

p2<=1'b0;

p1<=1'b0;

p0<=1'b0;

o_rdy1_reg<=1'b0;

end

else

begin

if(ena)

begin

cnt_4<=cnt_4+3'd1;

p0<=i_SPAD_out;

p1<=p0;

p2<=p1;

p3<=p2;

if(cnt_4==3'd4)

begin

cnt_4<=3'd1;

cnt_7560<=cnt_7560+13'd1;

end

end

else if(cnt_7560==13'd7560)

begin

cnt_4<=3'd0;

cnt_7560<=13'd0;

o_rdy1_reg<=1'b1;

p2<=1'b0;

p1<=1'b0;

p0<=1'b0;

p3<=1'b0;

end

else if(!i_en)

begin

cnt_4<=3'd0;

cnt_7560<=13'd0;

o_rdy1_reg<=1'b0;

p2<=1'b0;

p1<=1'b0;

p0<=1'b0;

p3<=1'b0;

end

end

end

assign o_rdy1=o_rdy1_reg;

blk_mem_gen_spadbuffer RAM1 (

.clka(clk), // input wire clka

.ena(ena), // input wire ena

.wea(wea), // input wire [0 : 0] wea

.addra(cnt_7560), // input wire [12 : 0] addra

.dina(w_data), // input wire [3 : 0] dina

.clkb(clk), // input wire clkb

.enb(enb), // input wire ena

.addrb(i_r_addr), // input wire [12 : 0] addrb

.doutb(o_r_data) // output wire [3 : 0] doutb

);

endmodule

运行结果及报错内容

暂无

我的解答思路和尝试过的方法

见图片表示

我想要达到的结果