fpga串口发送的数据为什么仿真正确,串口调试工具上却不断的显示00??

输出的uart接的ACX720的M15端口

顶层代码

`timescale 1ns / 1ps

module uart_tx_test(

Clk,

Reset_n,

uart_tx

);

input Clk;

input Reset_n;

output uart_tx;

reg Send_Go;

reg [7:0] Data;

wire Tx_done;

uart_byte_tx uart_byte_tx(

.Clk(Clk),

.Reset_n(Reset_n),

.Data(Data),

.Send_Go(Send_Go),

.Baud_set(3'd4),

.uart_tx(uart_tx),

.Tx_done(Tx_done)

);

reg [24:0] counter;

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

counter <= 0;

else if (counter == 4999999)

counter <= 0;

else

counter <= counter + 1;

end

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

Send_Go <= 0;

else if (counter == 1)

Send_Go <= 1;

else

Send_Go <= 0;

end

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

Data <= 0;

else if (Tx_done)

Data <= Data + 1;

end

endmodule

串口发送代码:

`timescale 1ns / 1ps

module uart_byte_tx(

Clk,

Reset_n,

Data,

Send_Go,

Baud_set,

uart_tx,

Tx_done

);

input Clk;

input Reset_n;

input [7:0]Data;

input Send_Go;

input [2:0]Baud_set;

output reg uart_tx;

output reg Tx_done;

//Baud_set = 0,则波特率 = 9600;

//Baud_set = 1,则波特率 = 19200;

//Baud_set = 2,则波特率 = 38400;

//Baud_set = 3,则波特率 = 57600;

reg [17:0] bps_DR;

reg [17:0] div_cnt;

reg Send_en;

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

Send_en <= 0;

else if (Send_Go)

Send_en <= 1;

else if (Tx_done)

Send_en <= 0;

end

reg [7:0] r_data;

always @(posedge Clk)

begin

if (Send_Go)

r_data <= Data;

else

r_data <= r_data;

end

wire bps_clk;

assign bps_clk = (div_cnt == 1);

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

div_cnt <= 0;

else if (Send_en)

begin

if(div_cnt == bps_DR - 1)

div_cnt <= 0;

else

div_cnt <= div_cnt + 1;

end

else

div_cnt <= 0;

end

always @(*)

begin

case (Baud_set)

0: bps_DR = 1000000000/9600/20;

1: bps_DR = 1000000000/19200/20;

2: bps_DR = 1000000000/38400/20;

3: bps_DR = 1000000000/57600/20;

4: bps_DR = 1000000000/115200/20;

default: bps_DR = 1000000000/9600/20;

endcase

end

reg [3:0] bps_cnt;

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

bps_cnt <= 0;

else if (Send_en)

begin

if (div_cnt == 1)

begin

if (bps_cnt == 11)

bps_cnt <= 0;

else

bps_cnt <= bps_cnt + 1;

end

else

bps_cnt <= bps_cnt;

end

else

bps_cnt <= 0;

end

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

begin

uart_tx <= 1'b1;

Tx_done <= 1'b0;

end

else

begin

case (bps_cnt)

0: begin

Tx_done <= 0;

uart_tx <= uart_tx;

end

1: uart_tx <= 0;

2: uart_tx <= r_data[0];

3: uart_tx <= r_data[1];

4: uart_tx <= r_data[2];

5: uart_tx <= r_data[3];

6: uart_tx <= r_data[4];

7: uart_tx <= r_data[5];

8: uart_tx <= r_data[6];

9: uart_tx <= r_data[7];

10: uart_tx <= 1;

11: uart_tx <= 1;

default: uart_tx <= 1;

endcase

end

end

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

Tx_done <= 1'b0;

else if (bps_clk == 1 && bps_cnt == 10)

Tx_done <= 1;

else

Tx_done <= 0;

end

endmodule

tb文件

`timescale 1ns / 1ps

module uart_tx_test_tb();

reg Clk;

reg Reset_n;

wire uart_tx;

uart_tx_test uart_tx_test(

.Clk(Clk),

.Reset_n(Reset_n),

.uart_tx(uart_tx)

);

initial Clk = 1;

always #10 Clk = ~Clk;

initial

begin

Reset_n = 0;

#201

Reset_n = 1;

#500000000;

$stop;

end

endmodule

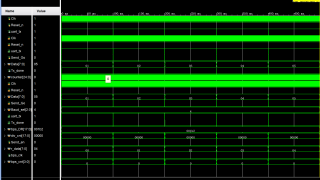

仿真图

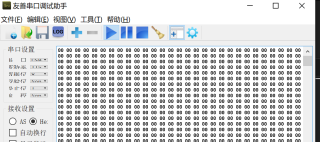

串口助手显示的数据

暂时没有想到问题出在哪,想请各位用我的代码试一试