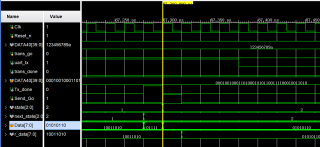

这种写法错哪里了呢,为什么这个Data会只维持一个时钟周期后又变了

状态机代码:

`timescale 1ns / 1ps

module uart_tx_data(

Clk,

Reset_n,

DATA40,

trans_go,

uart_tx,

trans_done

);

input Clk;

input Reset_n;

input trans_go;

input [39:0]DATA40;

output uart_tx;

output trans_done;

reg [7:0]Data;

reg Send_Go;

wire Tx_done;

uart_byte_tx uart_byte_tx(

.Clk(Clk),

.Reset_n(Reset_n),

.Data(Data),

.Send_Go(Send_Go),

.Baud_set(3'd4),

.uart_tx(uart_tx),

.Tx_done(Tx_done)

);

reg [2:0]state, next_state;

parameter IDLE = 0, send1 = 1, send2 = 2, send3 = 3, send4 = 4, send5 = 5;

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

Send_Go <= 0;

else if (Tx_done)

Send_Go <= 1;

else if (trans_go)

Send_Go <= 1;

else

Send_Go <= 0;

end

always @(*)

begin

case (state)

0: begin

if (trans_go) begin

Data = DATA40[7:0];

next_state = 1;

end

else begin

Data = Data;

next_state = 0;

end

end

1: begin

if (Tx_done) begin

Data = DATA40[15:8];

next_state = 2;

end

else

begin

Data = Data;

next_state = 1;

end

end

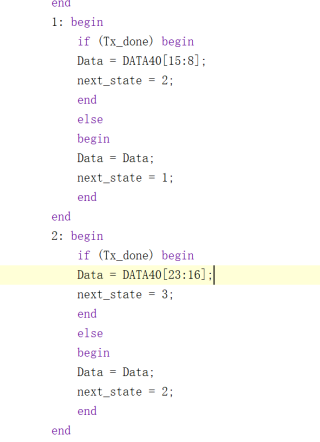

2: begin

if (Tx_done) begin

Data = DATA40[23:16];

next_state = 3;

end

else

begin

Data = Data;

next_state = 2;

end

end

3: begin

if (Tx_done) begin

Data = DATA40[31:24];

next_state = 4;

end

else

begin

Data = Data;

next_state = 3;

end

end

4: begin

if (Tx_done) begin

Data = DATA40[39:32];

next_state = 5;

end

else

begin

Data = Data;

next_state = 4;

end

end

5: begin

if (Tx_done)

next_state = 0;

else begin

next_state = 5;

end

end

default:begin

next_state = 0;

Data = 0;

end

endcase

end

always @(posedge Clk or negedge Reset_n)

begin

if (!Reset_n)

state = 0;

else

state = next_state;

end

assign trans_done = (state == 5 && Tx_done == 1);

endmodule