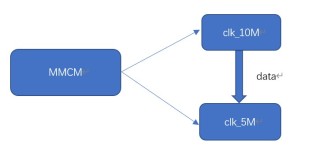

如图,时钟IP生成的不同时钟,时钟1对时钟2有数据发送,所以我想实现时钟1到时钟2的时序约束

所以写入时钟约束

set_false_path -from [get_clocks clk_10M_clk_wiz_0] -to [get_clocks clk_5M_clk_wiz_0]

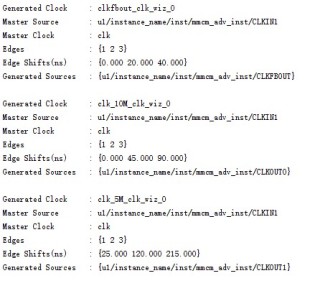

查看report_clocks

发现已经生成了时钟

但Vivado还是警告

[Vivado 12-627] No clocks matched 'clk_10M_clk_wiz_0'.

[Vivado 12-627] No clocks matched 'clk_5M_clk_wiz_0'.

查阅资料发现综合的时候未生成相应管脚,所以会有此警告,布局布线后可解决

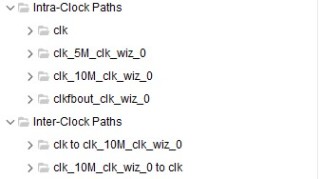

但我Implementation过后,再次生成时序约束报告,还是没有实现时钟1到时钟2的约束。

请问是哪里出了问题呢