课程实践,编写简单的模13奇数分频器

编写程序实在找不出来什么问题,但是仿真始终没有波形

这是分频器的代码

module fenpin13

(input clk,reset,

output wire cout);

reg [4:0]m,n;

reg cout1,cout2;

assign cout=cout1|cout2;

always @(posedge clk)

begin if(!reset) begin cout1<=0;m<=0;end

else

begin if(m==12) m<=0;else m<=m+1;

if(m<6) cout1<=1;else cout1<=0;

end

end

always @(posedge clk)

begin if(!reset) begin cout2<=0;n<=0;end

else begin

if(n==12) n<=0;else n<=n+1;

if(n<6) cout2<=1;else cout2<=0;end

end

endmodule

这是testbench文件的代码

`timescale 1ns/1ns

module fenpin13_tb;

reg clk,reset;

wire cout,cout1,cout2;

wire [4:0]m,n;

fenpin13 u1(clk,reset,cout);

parameter PERIOD=100;

initial

begin

reset=0;clk=0;

#40 reset=1;

forever

#(PERIOD/2) clk=~clk;

end

endmodule

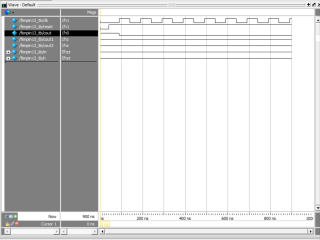

最后运行modelsim始终无波形

本人是初学者,希望可以多指教,谢谢!