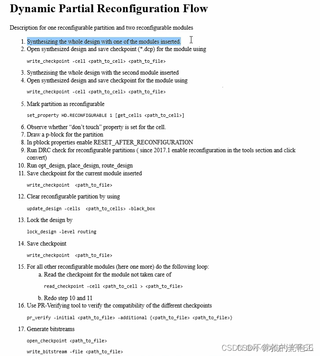

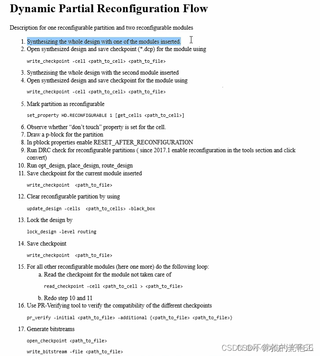

我现在根据网上的DPR流程,看的这个视频https://www.bilibili.com/video/BV1nW41137MQ/?spm_id_from=333.337.search-card.all.click

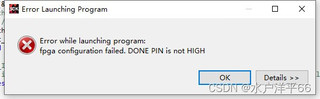

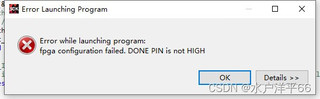

生成了相关的全部位流文件和部分位流文件,但是在我链接到SDK之后发现只能同时加载一个位流文件,再加载部分位流文件之后系统提示done引脚为低电平,无法继续写入,这该怎么办。(视频中使用pynq板子结合python验证的,我想用SDK验证)

我现在根据网上的DPR流程,看的这个视频https://www.bilibili.com/video/BV1nW41137MQ/?spm_id_from=333.337.search-card.all.click

生成了相关的全部位流文件和部分位流文件,但是在我链接到SDK之后发现只能同时加载一个位流文件,再加载部分位流文件之后系统提示done引脚为低电平,无法继续写入,这该怎么办。(视频中使用pynq板子结合python验证的,我想用SDK验证)

关注

关注参考AI提供:

对于使用Vivado和SDK进行DPR(动态部分重配置)的过程,一般我们首先在Vivado中完成硬件设计和部分重配置模块的分区等步骤,然后在SDK中进行位流的加载和部分重配置。

在SDK中,我们通常使用Xilinx的PCAP(Processor Configuration Access Port)接口来执行部分重配置。PCAP接口允许处理器通过AXI接口访问配置逻辑,执行全配置或部分配置。

一般在执行部分重配置之前,我们需要先将全局位流加载到FPGA中。然后根据需要,将部分位流写入到在全局位流中预留的partiton区域中。

关于你的问题,你需要确定以下几个环节:

全局位流文件已经正确地加载到FPGA中。

部分位流文件是正确地生成的,确保部分位流只包括在Vivado中定义的PR(Partial Reconfiguration)区域的配置信息。

用于部分重配置的硬件接口(PCAP)是正确配置的。

请验证你的硬件设计和位流文件,并确定在加载部分位流前,全局位流已经正确加载。

希望这些信息对你有所帮助,如果问题仍然存在,你可能需要检查你的硬件设计或者咨询Xilinx的技术支持。