HDLBits中的一道题目

假设这个状态机使用单次编码,其中状态[0]到状态[9]分别对应状态 S0 到 S9。除非另有说明,否则输出均为零

我的verilog代码是

```c

odule top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

parameter S0=10'b0000000001,

S1=10'b0000000010,

S2=10'b0000000100,

S3=10'b0000001000,

S4=10'b0000010000,

S5=10'b0000100000,

S6=10'b0001000000,

S7=10'b0010000000,

S8=10'b0100000000,

S9=10'b1000000000;

always@(*)begin

next_state=S0;

case(state)

S0:begin

if(in)

next_state=S1;

else

next_state=S0;

end

S1:begin

if(in)

next_state=S2;

else

next_state=S0;

end

S2:begin

if(in)

next_state=S3;

else

next_state=S0;

end

S3:begin

if(in)

next_state=S4;

else

next_state=S0;

end

S4:begin

if(in)

next_state=S5;

else

next_state=S0;

end

S5:begin

if(in)

next_state=S6;

else

next_state=S8;

end

S6:begin

if(in)

next_state=S7;

else

next_state=S9;

end

S7:begin

if(in)

next_state=S7;

else

next_state=S0;

end

S8:begin

if(in)

next_state=S1;

else

next_state=S0;

end

S9:begin

if(in)

next_state=S1;

else

next_state=S0;

end

endcase

end

always@(*)begin

case(state)

S7:begin

out1<=0;

out2<=1;

end

S8:begin

out1<=1;

out2<=0;

end

S9:begin

out1<=1;

out2<=1;

end

default:begin

out1<=0;

out2<=0;

end

endcase

end

endmodule

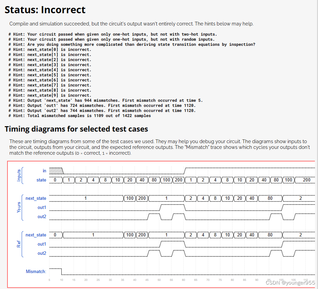

然后报错是

请教各位到底是什么原因导致的