在参考的这个开源SDI 转 MIPI 设计时,遇到了两个问题:https://antmicro.com/blog/2023/02/open-source-fpga-designs-for-the-sdi-to-mipi-csi-2-bridge/。

我在使用 CMOS 转 MIPI D-PHY IP 核时遇到了两个麻烦问题,有两个疑问希望能够解决:

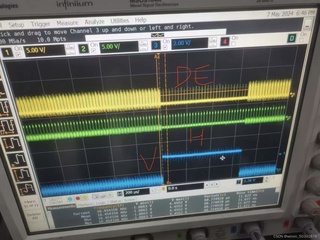

1.在使用 CrossLink-LIF-MD6000 型 FPGA 的 CMOS 转 MIPI D-PHY IP 核功能时,由GS2917A输出的输入信号 HSync、VSync、DE波形似乎正常(请参考示波器图像)。

但IP核输出数据和 CLK 时钟均为高电平。请问为什么输出的是高电平?可以从哪些方面去寻找错误解决IP核输出错误问题?

2. 是否可以使用 Reveal 观察 IP 核的各种信号(输入、输出等)?

如果可以,如何进行观察?

来自摄像机的 SDI 信号由 GS2917A 转换成 DOUT[19-10]数据 和HSync、VSync、DE的时钟,然后输入到 CrossLink-LIF-MD6000 中,调用IP核。

然而,CrossLink-LIF-MD6000 的 DPHY 和 CLK 输出均为高电平。

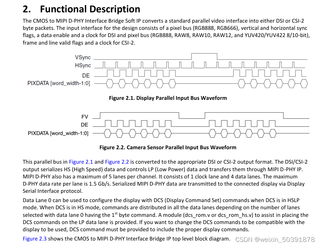

关于 CMOS 转 MIPI D-PHY IP 核的技术手册:https://www.latticesemi.com/Search.aspx?&lcid=9&q=FPGA-IPUG-02007&t=480