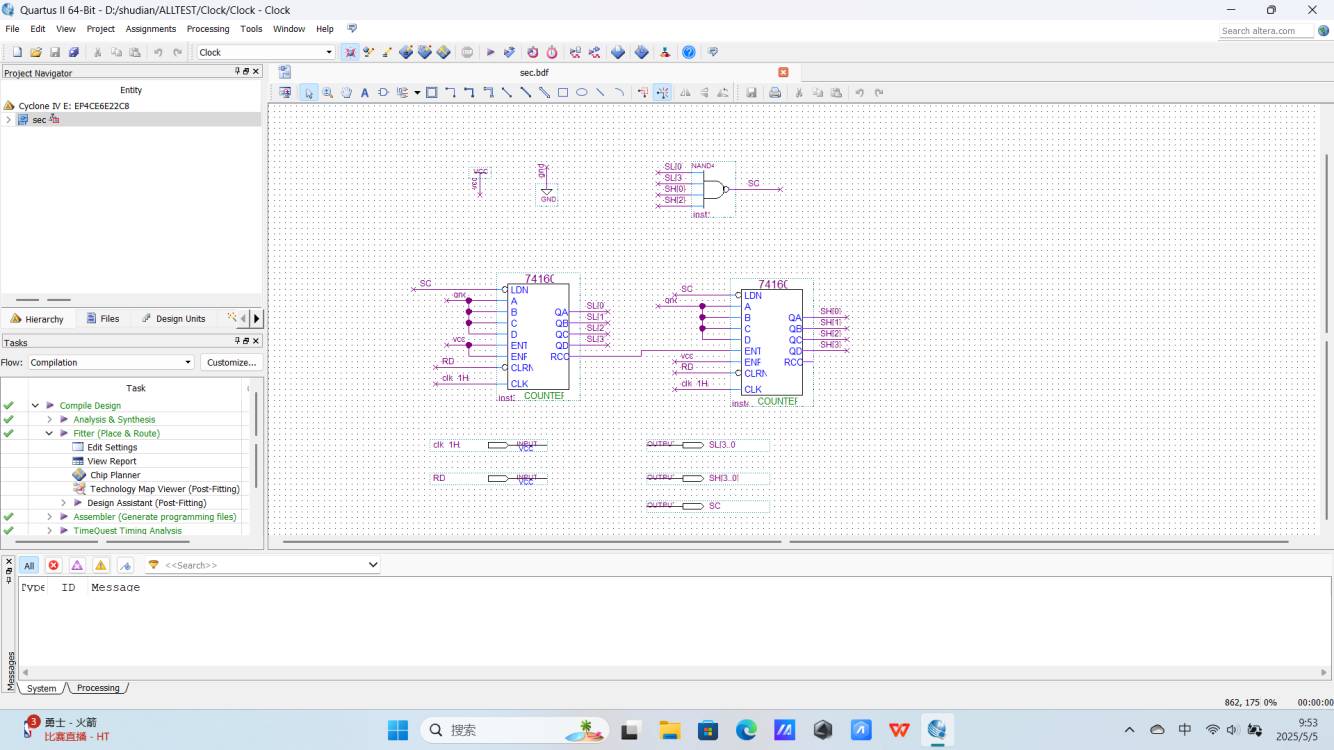

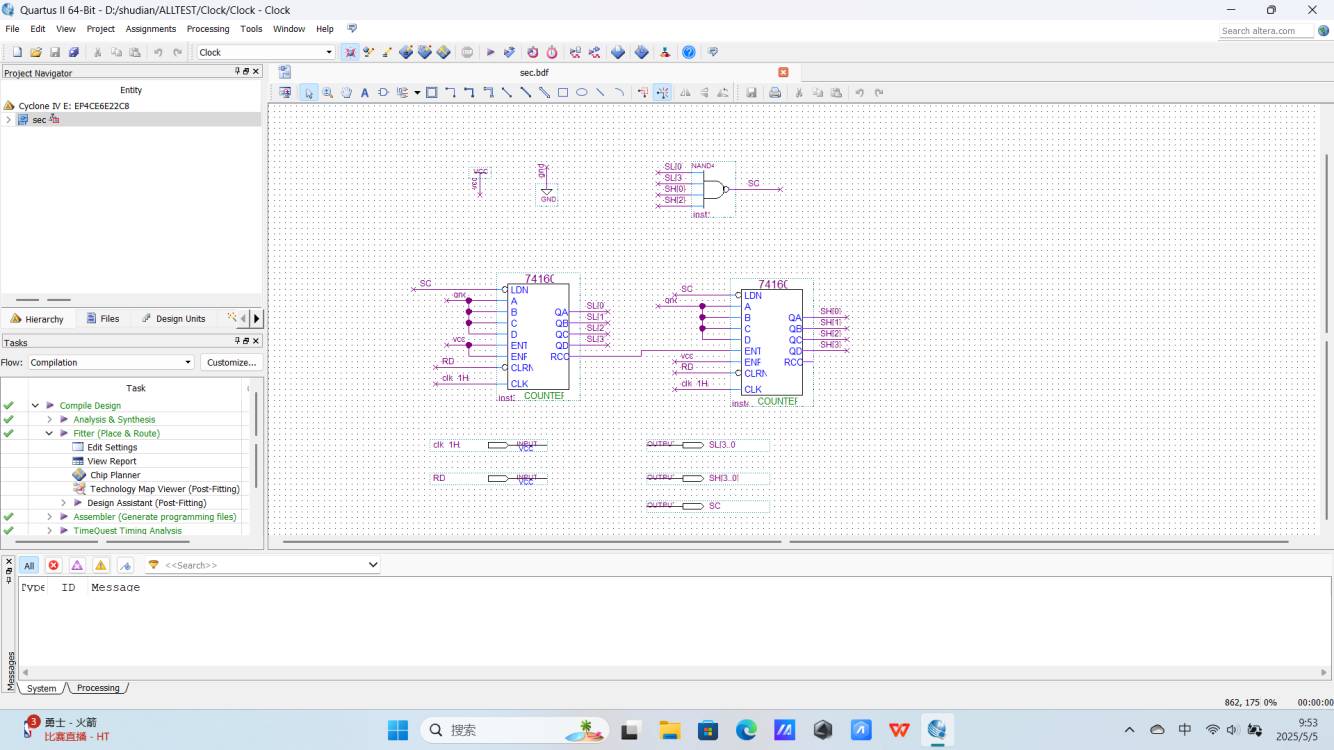

如图为输入的原理图,功能为60进制计数器,应该是没有问题的,编译的时候也没有报错。

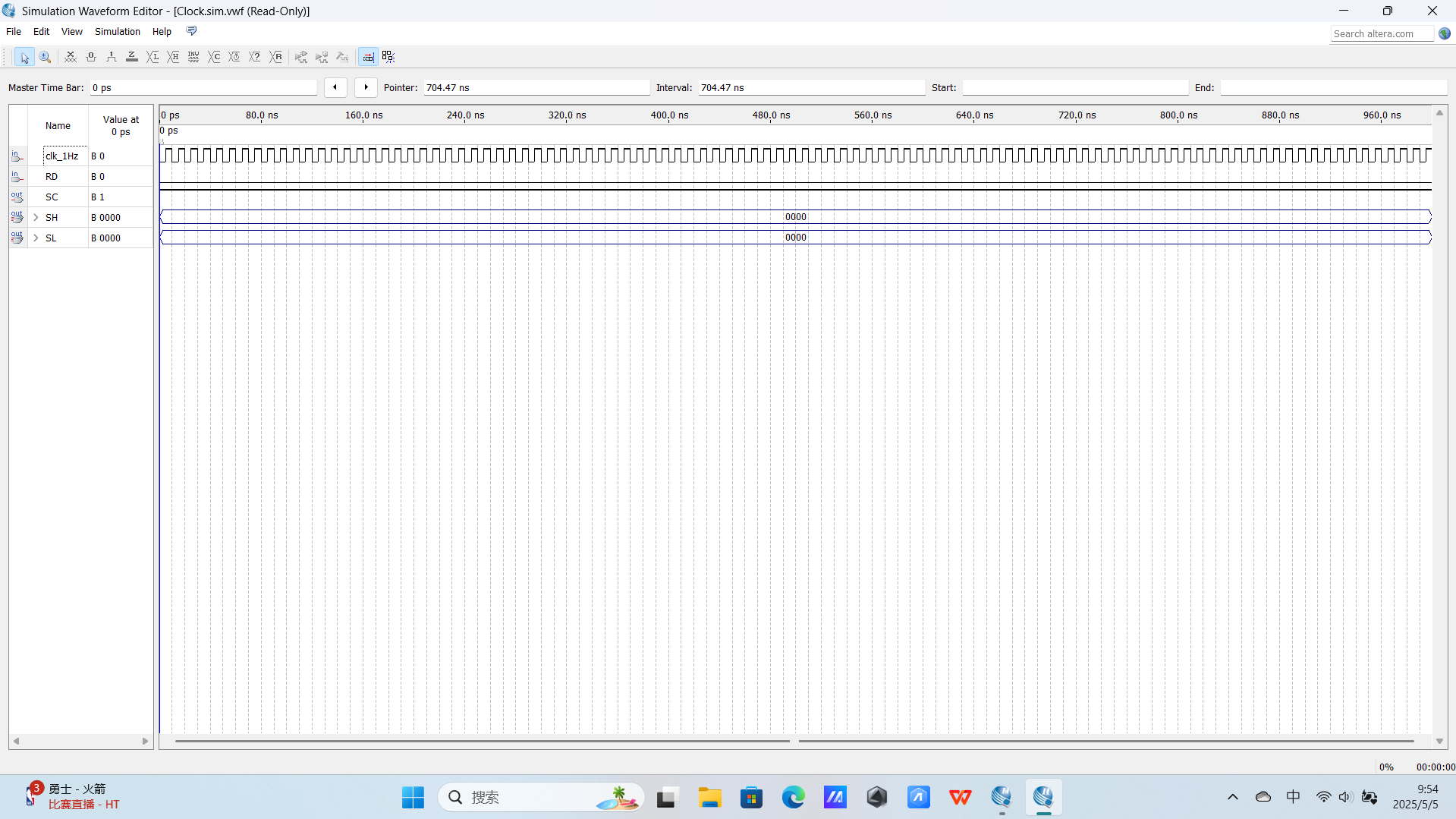

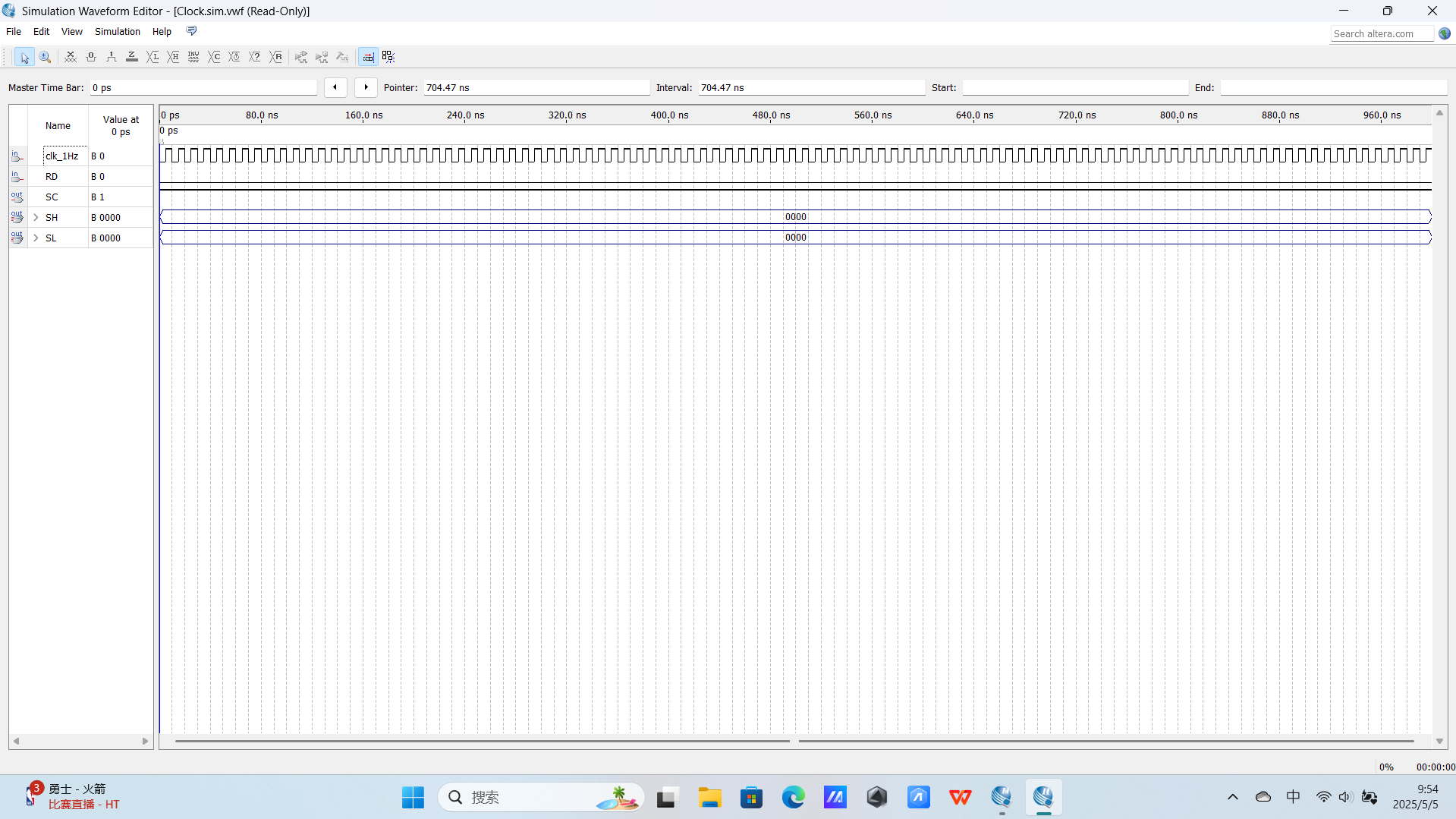

在进行电路仿真时却没有出现想要的结果,是哪里有问题吗?软件为quartusii。

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

你遇到的问题是,在使用Quartus II进行数电设计时,编译没有报错,但是电路仿真却没有出现想要的结果。下面是一些可能的解决方案:

如果以上解决方案都不能解决问题,可以提供更多的信息和设计文件,以便更好地帮助你解决问题。

-- 60进制计数器的 VHDL 代码

library IEEE;

use IEEE.STD_LOGIC;

use IEEE.NUMERIC_STD.ALL;

entity counter_60 is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

count : out STD_LOGIC_VECTOR (5 downto 0));

end counter_60;

architecture Behavioral of counter_60 is

signal count_int : unsigned(5 downto 0) := (others => '0');

begin

process(clk, reset)

begin

if reset = '1' then

count_int <= (others => '0');

elsif rising_edge(clk) then

count_int <= count_int + 1;

end if;

end process;

count <= std_logic_vector(count_int);

end Behavioral;

硬件工程, FPGA 开发