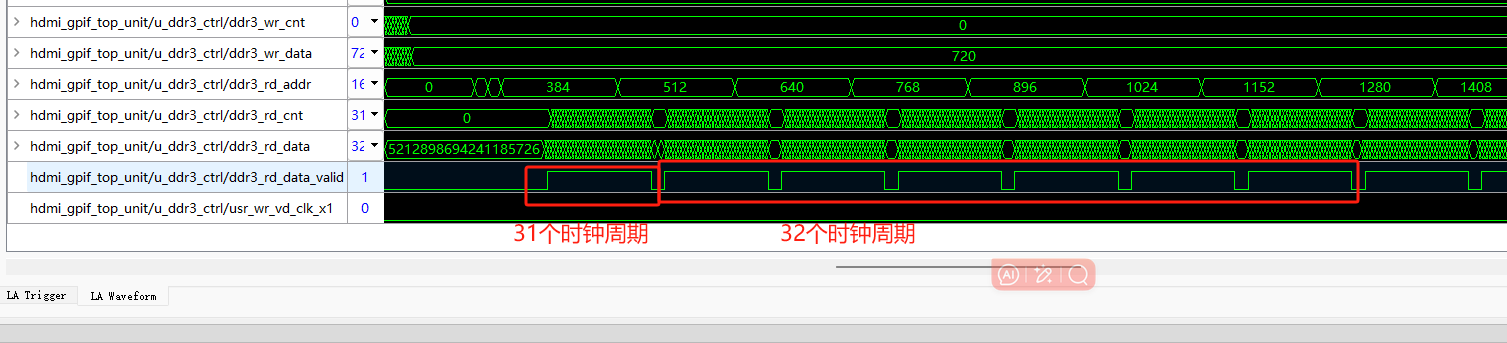

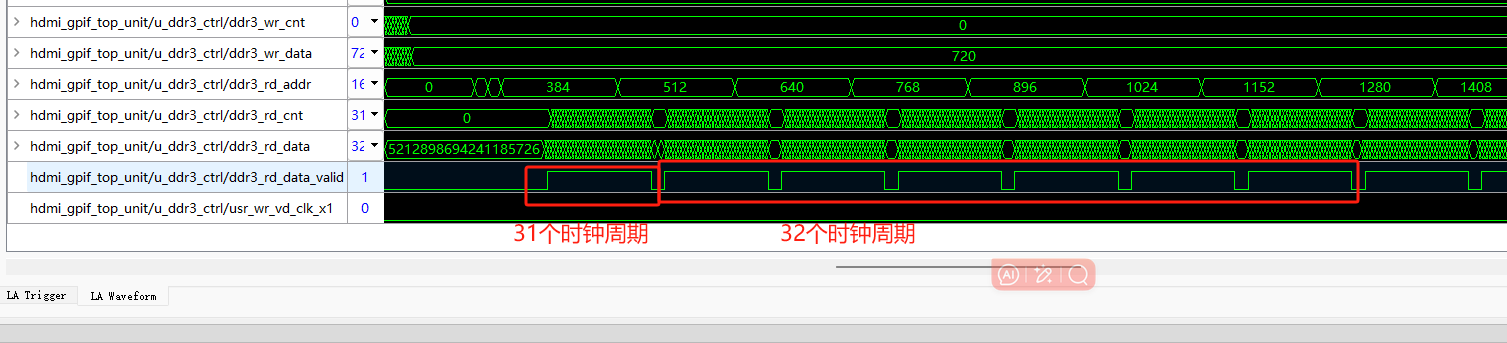

请教一下各位,用lattice fpga进行ddr读写测试时遇到一个问题,在读的时候,read_data_valid信号跟后面的时间长度不一致,第一个只有31个时钟周期,后面read_data_valid都是32个,可能是什么原因导致的,型号是ECP5U系列

请教一下各位,用lattice fpga进行ddr读写测试时遇到一个问题,在读的时候,read_data_valid信号跟后面的时间长度不一致,第一个只有31个时钟周期,后面read_data_valid都是32个,可能是什么原因导致的,型号是ECP5U系列

关注

关注让 “紫雾凌寒” 来帮你回答,本回答结合 DeepSeek

如果还有问题,请评论或点击头像私信,如果有帮助到您, 请关注、采纳、点赞

read_data_valid信号的持续时间不一致。第一个read_data_valid信号持续31个时钟周期,后续的情况未完整说明,但可以推测是持续时间存在异常。这可能涉及到DDR控制器的配置、时序设置以及与FPGA逻辑的交互问题。module ddr_controller (

input wire clk,

input wire rst_n,

// 与DDR芯片连接的接口信号

output reg [DDR_ADDR_WIDTH - 1:0] addr,

output reg [DDR_DATA_WIDTH - 1:0] wr_data,

input wire [DDR_DATA_WIDTH - 1:0] rd_data,

output reg wr_en,

output reg rd_en,

output reg [DDR_BURST_LEN - 1:0] burst_len,

// 与FPGA逻辑交互的信号

output reg read_data_valid,

input wire read_start

);

// DDR控制器IP核的实例化

ddr_ip_core u1 (

.clk(clk),

.rst_n(rst_n),

.addr(addr),

.wr_data(wr_data),

.rd_data(rd_data),

.wr_en(wr_en),

.rd_en(rd_en),

.burst_len(burst_len)

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

read_data_valid <= 0;

end else if (read_start) begin

read_data_valid <= 1;

// 根据DDR控制器的配置,设置合适的读数据持续时间

// 例如,如果突发长度为8,每个突发周期持续8个时钟周期

// 这里假设突发长度固定,实际可能需要动态计算

// 持续时间的计算可以根据DDR控制器的手册来确定

// 以下是一个简单示例,持续时间为突发长度个时钟周期

if (burst_len == 8) begin

#8;

read_data_valid <= 0;

end

end

end

endmodule

# 设置DDR时钟约束

create_clock -name ddr_clk -period 10.0 [get_ports ddr_clk]

# 设置与DDR时钟相关的建立时间和保持时间约束

set_input_delay -clock ddr_clk -min 0.5 [get_ports ddr_addr[*]]

set_input_delay -clock ddr_clk -max 1.5 [get_ports ddr_addr[*]]

set_output_delay -clock ddr_clk -min 0.5 [get_ports ddr_wr_data[*]]

set_output_delay -clock ddr_clk -max 1.5 [get_ports ddr_wr_data[*]]

read_data_valid有效期间,能够正确地读取和处理数据。read_data_valid信号持续时间不一致的问题,需要从DDR控制器配置、时序约束以及FPGA逻辑与DDR控制器交互这几个方面进行全面排查。通过正确设置参数、调整时序关系以及检查逻辑交互,可以解决DDR读写测试中出现的此类问题,确保DDR读写的正确性和稳定性。需要注意的是,以上代码和示例仅为参考,实际应用中需要根据具体的FPGA型号、DDR芯片规格以及项目需求进行调整和优化。

希望以上解答对您有所帮助。如果您有任何疑问,欢迎在评论区提出。