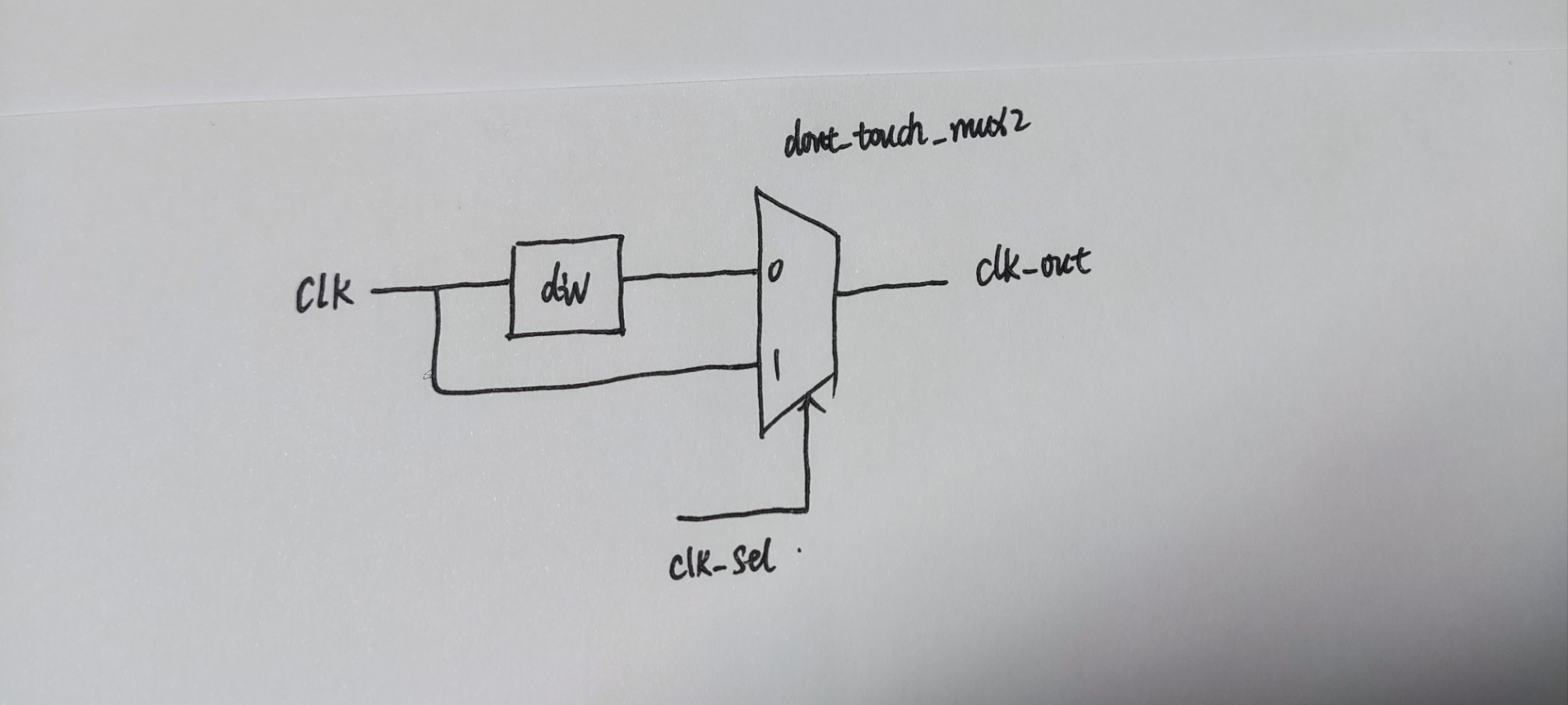

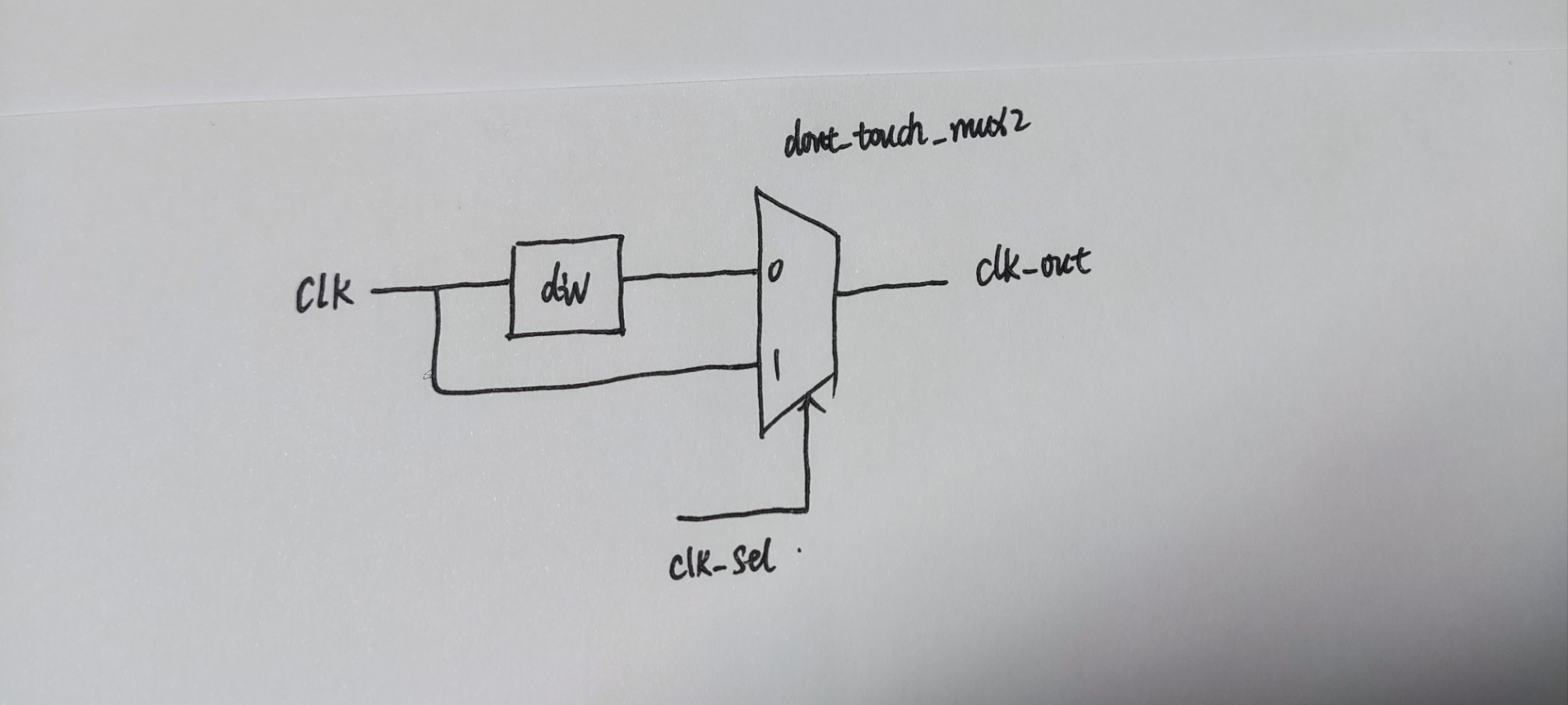

请教个问题。对于分频时钟约束,clk是主时钟,衍生出一个可分频时钟(最大频率为不分频)。

约束时,采用create_generated_clock -name clk_out -source [get_ports clk] [get_pins xx/O]这样示例

。

在apr cts分析setup时序时,发现launch路径走了clk_div路径,路径较长;capture路径走了未分频的路径。这个时序分析,clock的路径混乱,这种情况,应该怎么处理?

请教个问题。对于分频时钟约束,clk是主时钟,衍生出一个可分频时钟(最大频率为不分频)。

约束时,采用create_generated_clock -name clk_out -source [get_ports clk] [get_pins xx/O]这样示例

。

在apr cts分析setup时序时,发现launch路径走了clk_div路径,路径较长;capture路径走了未分频的路径。这个时序分析,clock的路径混乱,这种情况,应该怎么处理?

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

你遇到了时序路径错误问题,可能是由于分频时钟约束不正确或时序路径分析不准确导致的。

根据你的描述,使用 create_generated_clock 命令创建了一个可分频时钟 clk_out,并将其约束到主时钟 clk。但是,仍然出现时序路径错误问题。

以下是一些可能的解决方案:

create_generated_clock 命令正确地创建了时钟约束,并且约束的路径正确。aprun 命令来分析时序路径,检查是否存在时序路径错误。以下是一个示例代码,用于创建可分频时钟:

create_generated_clock -name clk_out -source [get_clocks clk] -divide_by 2

其中,clk 是主时钟,clk_out 是可分频时钟,divide_by 2 表示将主时钟分频到可分频时钟的频率为主时钟的1/2。

如果你仍然遇到时序路径错误问题,可以提供更多的信息和代码,帮助我更好地分析和解决问题。