下午好🌅🌅🌅

本答案参考通义千问

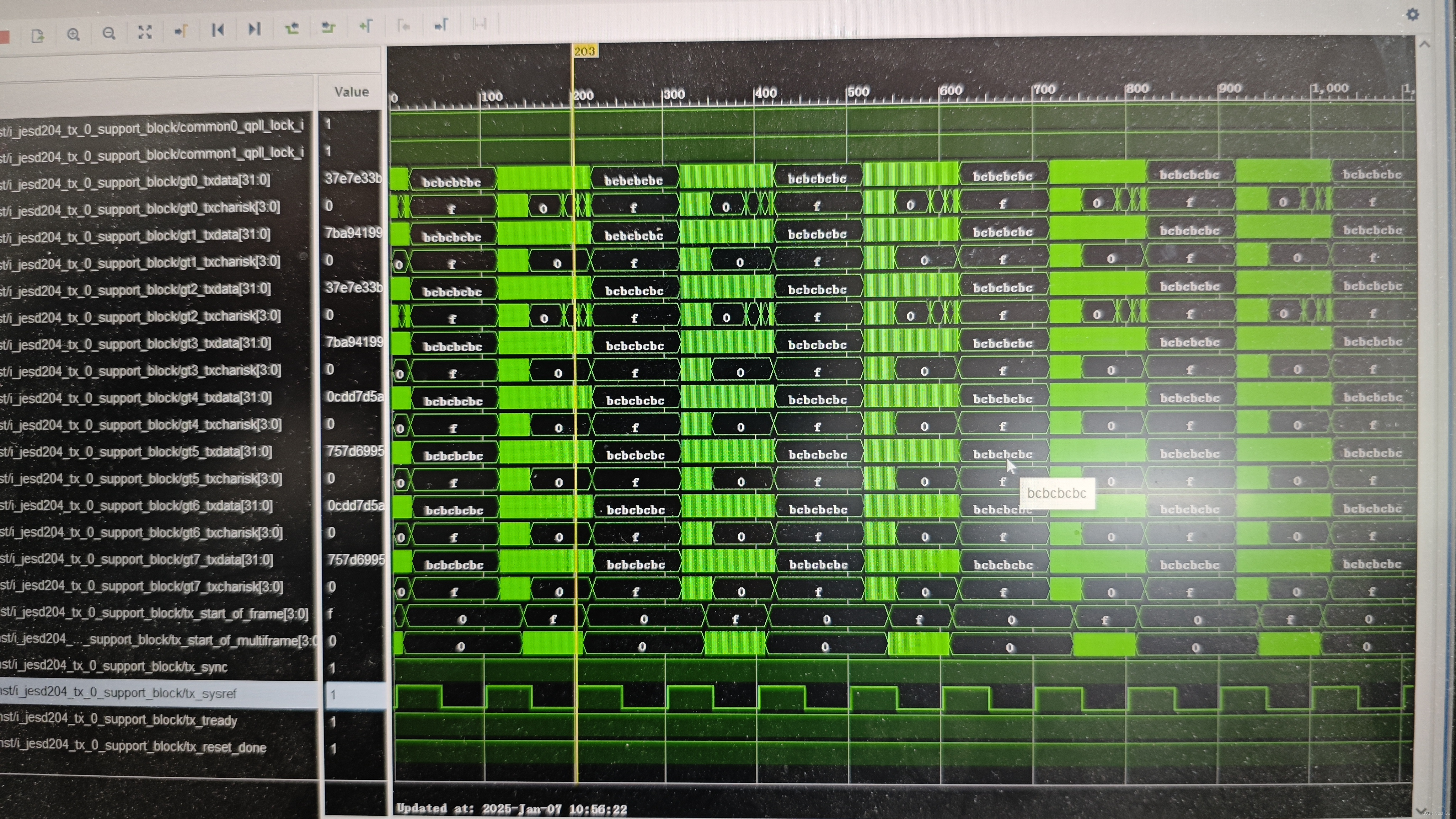

在调试AD9176时,如果发现JESD204B链路发送一段数据后,接着发送一段BCBC(Block Control Code),然后循环这样子,这通常表明JESD204B链路配置或同步过程中出现了问题。以下是可能的原因和详细的解决方案:

一、可能的原因分析

1. JESD204B链路未正确对齐(Alignment)

- JESD204B协议要求设备之间进行严格的时钟同步和通道对齐。

- 如果对齐失败,可能会导致部分通道数据丢失或被填充为BCBC(Block Control Code)。

2. 时钟同步异常(Clock Synchronization)

- JESD204B依赖于主从时钟同步机制,如果主时钟(如参考时钟)不稳定或与从设备不同步,会导致数据传输错误。

- BCBC的出现可能是由于时钟漂移或相位偏移引起的。

3. 通道配置不匹配(Channel Configuration Mismatch)

- AD9176的JESD204B接口需要与FPGA或其他接收端设备在通道数、采样率、数据位宽、Lane数等参数上完全一致。

- 如果参数不匹配,系统可能会自动填充BCBC来保持链路稳定。

4. 帧结构错误(Frame Structure Errors)

- JESD204B链路中的帧头(Frame Header)和帧尾(Frame Tail)定义了数据的结构。

- 如果帧结构错误或缺失,接收端无法解析数据,可能会误判为BCBC。

5. Link Layer协议层错误(Link Layer Error)

- JESD204B协议中有一个**Link Layer(链路层)**用于控制数据流。

- 如果链路层检测到错误(如CRC校验失败、同步丢失等),会触发BCBC插入。

二、解决步骤(有序列表)

1. 检查并确保JESD204B链路正确对齐

- 使用示波器或逻辑分析仪检查JESD204B的TX和RX时钟是否对齐。

- 确保MCLK(Master Clock)和LCLK(Link Clock)频率一致,并且相位关系正确。

2. 验证时钟源稳定性

- 使用高精度时钟源(如晶振或PLL)作为参考时钟。

- 检查JESD204B的时钟抖动是否在允许范围内(通常应小于100ps)。

3. 核对JESD204B参数配置

- 在AD9176的寄存器中检查以下关键参数:

- Lane数(Number of Lanes)

- 每通道数据位宽(Bits per Sample)

- 采样率(Sample Rate)

- Subclass模式(Subclass 1 or 2)

- 确保这些参数与FPGA或接收端设备配置一致。

4. 检查帧结构和帧头设置

- 使用JESD204B分析工具(如ADI提供的JESD204B Analyzer)检查帧头(Frame Header)和帧尾(Frame Tail)是否正确。

- 确保帧结构符合JESD204B标准,例如:Frame Size = N * K / (M * L),其中:

- N: 通道数

- K: 每帧样本数

- M: 每个通道的数据位宽

- L: Lane数

5. 检查Link Layer状态和错误标志

- 查看AD9176的Link Status寄存器,确认是否有错误标志(如Sync Lost, CRC Error等)。

- 如果有错误,需根据具体错误类型进行排查。

三、代码示例(AD9176初始化代码片段)

以下是一个简化的AD9176初始化代码示例(基于I2C通信):

// 初始化AD9176的JESD204B配置

void AD9176_Init_JESD204B(void) {

// 设置Lane数量(例如:2 lanes)

AD9176_WriteReg(0x0A, 0x02); // Reg 0x0A: Lane Count = 2

// 设置每个通道的数据位宽(例如:14 bits)

AD9176_WriteReg(0x0B, 0x0E); // Reg 0x0B: Bits per Sample = 14

// 设置采样率(例如:125 Msps)

AD9176_WriteReg(0x0C, 0x08); // Reg 0x0C: Sample Rate = 125 Msps

// 设置Subclass模式(Subclass 1)

AD9176_WriteReg(0x0D, 0x01); // Reg 0x0D: Subclass = 1

// 启用JESD204B Link

AD9176_WriteReg(0x0F, 0x01); // Reg 0x0F: Enable JESD204B Link

}

注意: 上述代码仅为示例,实际寄存器地址和值需参考AD9176的数据手册。

四、建议工具和资源

- JESD204B Analyzer(如ADI提供的工具):用于分析JESD204B链路的同步状态和数据流。

- 示波器/逻辑分析仪:用于观察JESD204B的TX/RX信号和时钟。

- AD9176数据手册:详细说明寄存器配置和JESD204B参数设置。

五、总结

| 原因 | 解决方案 |

|------|----------|

| 链路未对齐 | 检查TX/RX时钟同步,使用示波器验证 |

| 时钟不稳定 | 使用高精度时钟源,检查时钟抖动 |

| 参数配置不一致 | 核对AD9176与接收端的JESD204B配置 |

| 帧结构错误 | 使用JESD204B分析工具检查帧头和帧尾 |

| Link Layer错误 | 检查Link Status寄存器,排除CRC或同步错误 |

如果你能提供更具体的配置信息(如Lane数、采样率、数据位宽等),我可以进一步帮你定位问题。