下午好🌅🌅🌅

本答案参考通义千问

你好!你提到的是一个关于使用 Synopsys VCS 进行数字IC设计验证的实践项目复现问题。这是一个非常有意义的尝试,尤其是在学习数字电路设计和验证流程方面。

下面我将针对你的两个问题进行详细解答,并提供相应的建议与操作步骤,帮助你更好地理解和复现该项目。

一、问题一:VCS部分的验证结果图应该怎么解读?

✅ 重点理解:

VCS(Verdi Compiler System) 是 Synopsys 提供的一种强大的仿真和调试工具,用于查看和分析数字电路的行为,特别是在 RTL 级或门级仿真中。

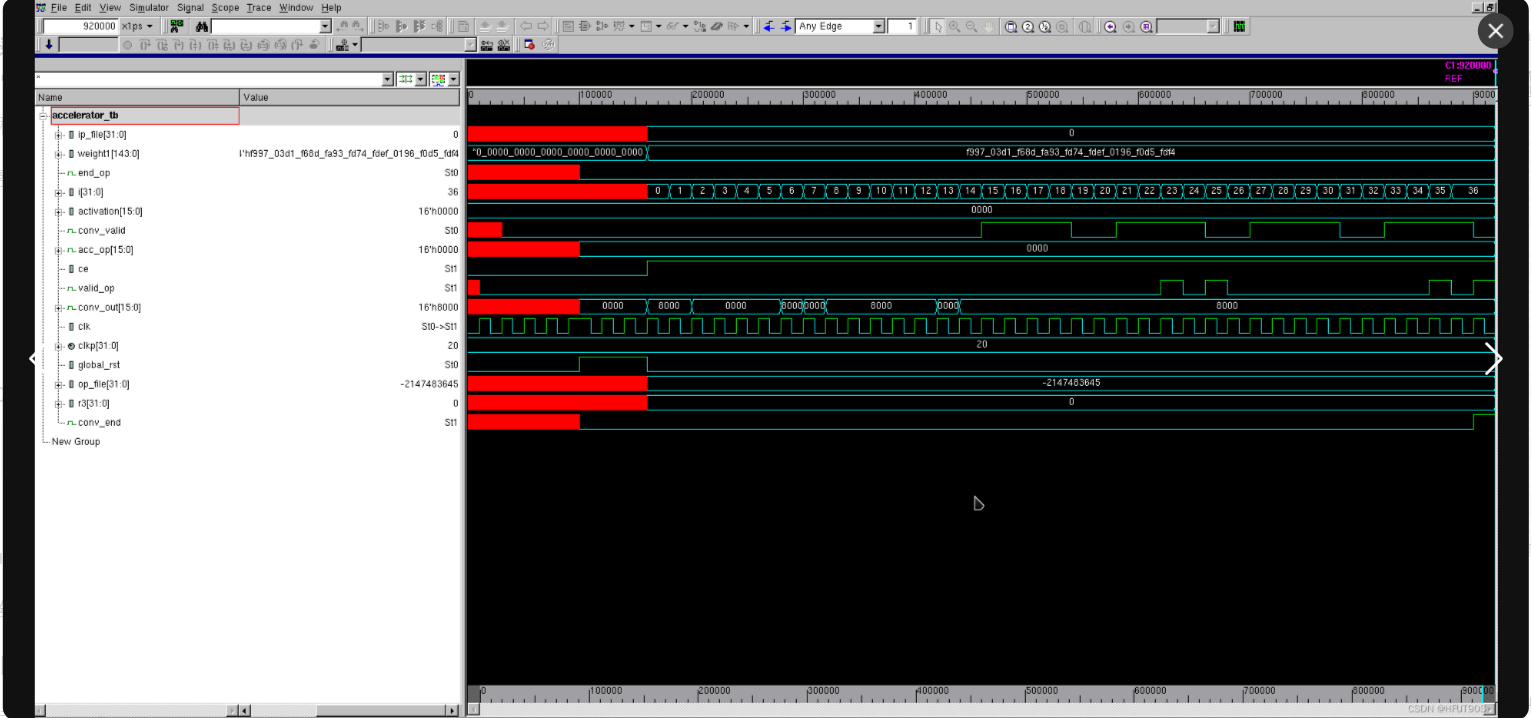

在文章中提到的“验证结果图”,可能是指通过 VCS/Verdi 工具显示的波形图(Waveform),用来展示信号随时间的变化情况。

✅ 如何解读波形图?

-

时间轴(Time Axis)

- 横坐标表示时间,通常以 ns(纳秒)为单位。

- 你可以看到各个信号在不同时间点的状态变化。

-

信号名(Signal Names)

- 列出的是你关注的信号名称,例如

clk, rst_n, data_in, conv_result 等。 - 有些信号可能是模块内部的,比如

regfile[0], add_out 等。

-

信号状态(Signal Values)

- 用不同的颜色或波形表示逻辑值(0、1、X、Z 等)。

- 例如,

clk 通常是周期性的方波,rst_n 在初始时为低电平(复位),之后变为高电平(正常运行)。

-

关键事件(Events)

- 通过观察信号变化可以判断模块是否按预期工作。

- 例如,输入数据

data_in 是否在 clk 上升沿被正确读取,输出 conv_result 是否在适当的时间出现。

-

波形缩放与定位(Zoom & Navigate)

- 使用 Verdi 的图形界面可以放大特定时间段,便于观察细节。

- 可以通过点击波形中的事件来跳转到对应的代码位置。

✅ 总结:

- 波形图是验证设计行为的关键手段。

- 通过观察关键信号(如时钟、复位、输入、输出)的变化,可以判断设计是否符合预期。

- 如果波形不符合预期,说明设计可能存在逻辑错误或时序问题。

二、问题二:如果我想修改输入再次验证的话,应该是怎样进行修改?在哪里进行修改?

✅ 重点理解:

要修改输入并重新验证,需要找到项目的 测试平台(Testbench) 文件,并对其进行修改。

✅ 修改步骤如下:

1. 确定测试平台文件(Testbench)

- 通常,测试平台文件会以

_tb.v 或 .vhd 结尾。 - 例如,在项目中可能有类似

cnn_accelerator_tb.v 的文件。

2. 打开测试平台文件

- 使用文本编辑器(如 VSCode、Notepad++)或 IDE 打开该文件。

- 查找以下内容:

- 输入信号定义(如

input [31:0] data_in;) - 初始化语句(如

initial begin) - 数据驱动逻辑(如

data_in = 32'h12345678;)

3. 修改输入数据

- 在

initial 块中,可以修改输入信号的赋值。 - 例如,将原来的

data_in = 32'h12345678; 改为 data_in = 32'hdeadbeef;

4. 保存并重新编译

- 使用 VCS 编译命令重新编译整个项目,确保修改生效。

5. 运行仿真并查看波形

- 再次运行 VCS 仿真,使用 Verdi 查看新的波形结果。

✅ 示例:修改测试平台文件

假设你有一个测试平台文件 cnn_accelerator_tb.v,其中包含如下代码:

module cnn_accelerator_tb;

reg clk;

reg rst_n;

reg [31:0] data_in;

wire [31:0] conv_result;

// 实例化被测模块

cnn_accelerator uut (

.clk(clk),

.rst_n(rst_n),

.data_in(data_in),

.conv_result(conv_result)

);

initial begin

// 初始化信号

clk = 0;

rst_n = 0;

data_in = 32'h12345678;

#10 rst_n = 1;

// 等待一段时间后停止

#100 $finish;

end

always #5 clk = ~clk;

endmodule

✅ 修改后的版本:

module cnn_accelerator_tb;

reg clk;

reg rst_n;

reg [31:0] data_in;

wire [31:0] conv_result;

// 实例化被测模块

cnn_accelerator uut (

.clk(clk),

.rst_n(rst_n),

.data_in(data_in),

.conv_result(conv_result)

);

initial begin

// 初始化信号

clk = 0;

rst_n = 0;

data_in = 32'hdeadbeef; // 修改输入数据

#10 rst_n = 1;

// 等待一段时间后停止

#100 $finish;

end

always #5 clk = ~clk;

endmodule

✅ 总结

| 问题 | 解答 |

|------|------|

| 问题一:VCS验证结果图怎么解读? | 通过观察波形图中的信号变化、时间轴、关键事件等,判断设计是否符合预期。 |

| 问题二:如何修改输入并重新验证? | 修改测试平台文件中的输入信号赋值,重新编译并运行仿真,使用 Verdi 查看新结果。 |

如果你愿意,我可以进一步帮你分析具体的波形图或测试平台代码,也可以提供更详细的 VCS 编译和仿真命令。

祝你项目顺利!如有其他问题,随时欢迎提问。