下午好🌅🌅🌅

本答案参考通义千问

你目前在使用Synopsys的VCS工具复现《数字IC实践项目(3)——卷积神经网络加速器》时遇到了一些问题,这是非常正常的,尤其是在刚开始接触数字IC开发和验证流程的时候。下面我将针对你的两个问题进行详细解答,并提供重点部分的加粗说明,以及解决方案的有序列表。

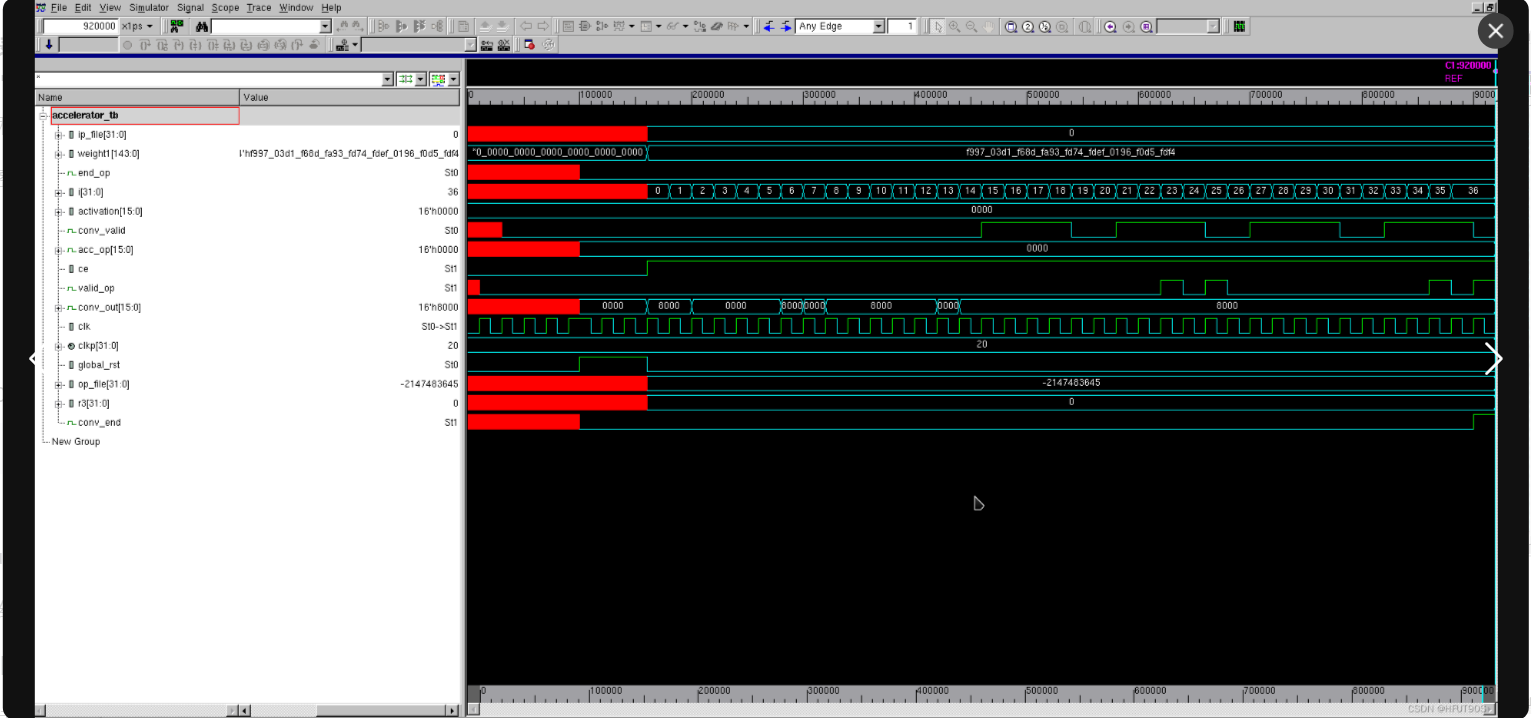

问题一:文中VCS部分的验证结果图应该怎么解读?

1. 验证结果图的作用

VCS(Verdi Compiler System)是Synopsys的一个仿真和调试工具,用于查看设计在仿真过程中的行为。验证结果图通常展示的是信号波形(Waveform),例如输入数据、控制信号、输出结果等。

2. 如何解读这些波形图?

- 时间轴(X轴):表示仿真的时间,单位通常是ns(纳秒)。

- 信号名称(Y轴):每个信号代表一个寄存器、总线或模块的输出。

- 信号状态:高电平(1)、低电平(0)、未知(X)或高阻态(Z)。

3. 举例说明

假设你在验证CNN加速器时,看到如下波形:

input_data[7:0]:表示输入的8位数据,在某个时刻从0x00变为0x55。conv_result[15:0]:表示卷积后的16位结果,在另一个时刻从0x0000变为0x1234。valid:表示该帧数据是否有效,为1时表示数据有效。

重点说明:

验证结果图的核心目的是确认设计在仿真中是否按照预期工作,比如输入是否被正确处理、输出是否符合预期、控制逻辑是否正确等。

4. 常见问题

- 如果波形没有变化,可能是仿真未运行完全。

- 如果输出不符合预期,可能需要检查设计逻辑或激励文件(testbench)是否正确。

问题二:如果我想修改输入再次验证的话,应该是怎样进行修改?在哪里进行修改?

1. 修改输入的位置

在大多数数字IC项目中,输入数据通常由**测试平台(Testbench)**生成。因此,修改输入的关键在于修改Testbench文件。

2. 具体步骤

步骤一:找到Testbench文件

- 在项目的源代码目录中查找类似

tb_*.v 或 testbench.v 的文件。 - 例如:

tb_cnn_accelerator.v。

步骤二:定位输入信号

- 打开Testbench文件,查找定义输入信号的部分,如:

reg [7:0] input_data;

- 查找驱动这些信号的代码,通常是在

initial 块中设置初始值。

步骤三:修改输入数据

步骤四:重新编译并运行VCS

总结与建议

重点总结:

- 验证结果图是用来观察设计在仿真中的行为,特别是输入、输出和控制信号的状态。

- 修改输入应通过修改Testbench文件实现,重点关注输入信号的初始化和赋值部分。

- 推荐使用VCS的图形界面(Verdi)来更直观地分析波形。

解决方案列表

-

理解VCS验证结果图的含义:

- 波形图展示的是设计在仿真过程中的信号变化。

- 检查输入、输出、控制信号是否符合预期。

-

定位并修改Testbench文件:

- 查找

tb_*.v 文件,定位输入信号定义和赋值部分。 - 修改

input_data 等信号的值。

-

重新编译并运行VCS:

- 使用

vcs 编译命令重新生成可执行文件。 - 使用

vcs -R 运行仿真,并通过Verdi查看波形。

-

使用Verdi调试工具:

-

参考项目文档:

- 如果项目有说明文件(如 README.md),可以查阅其中关于如何修改输入、运行测试等内容。

示例代码修改(Testbench部分)

如果你在 tb_cnn_accelerator.v 中发现如下代码:

initial begin

input_data = 8'h00;

#10;

input_data = 8'hFF;

#10;

input_data = 8'hAA;

end

你可以将其修改为:

initial begin

input_data = 8'h55; // 修改为新的输入值

#10;

input_data = 8'hAA;

#10;

input_data = 8'h00;

end

如果你需要进一步帮助,比如具体文件结构、编译命令或波形分析,请提供更多细节,我可以为你定制化指导!希望你能顺利复现项目!